# UNIVERSIDADE DO ESTADO DE SANTA CATARINA – UDESC CENTRO DE CIÊNCIAS TECNOLÓGICAS – CCT PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA – PPGEEL

**HENRIQUE THOMASELLI TEICHERT**

THE DUAL ACTIVE BRIDGE CONVERTER: A STUDY ON SPS MODULATION AND A CURRENT STRESS REDUCTION ALGORITHM FOR DPS MODULATION

JOINVILLE 2025

# UNIVERSIDADE DO ESTADO DE SANTA CATARINA – UDESC CENTRO DE CIÊNCIAS TECNOLÓGICAS – CCT PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA – PPGEEL

**HENRIQUE THOMASELLI TEICHERT**

O CONVERSOR DUAL ACTIVE BRIDGE: UM ESTUDO DA MODULAÇÃO SPS E

UM ALGORITMO DE REDUÇÃO DOS ESFORÇOS DE CORRENTE PARA

MODULAÇÃO DPS

JOINVILLE

# **HENRIQUE THOMASELLI TEICHERT**

# THE DUAL ACTIVE BRIDGE CONVERTER: A STUDY ON SPS MODULATION AND A CURRENT STRESS REDUCTION ALGORITHM FOR DPS MODULATION

Master's thesis presented to the Graduate Program in Electrical Engineering of the Santa Catarina State University, as requirement for obtention of the title of Master in Electrical Engineering, concentration area of Electronic Systems. Supervisor: Yales Rômulo de Novaes, Dr. Co-supervisor: Sandro Guenter, Dr.

JOINVILLE 2025

# Ficha catalográfica elaborada pelo programa de geração automática da Biblioteca Universitária Udesc, com os dados fornecidos pelo(a) autor(a)

Teichert, Henrique

The Dual Active Bridge Converter: A Study on SPS Modulation and a Current Stress Reduction Algorithm for DPS Modulation / Henrique Teichert. -- 2025.

197 p.

Orientador: Yales Rômulo de Novaes Coorientador: Sandro Guenter

Dissertação (mestrado) -- Universidade do Estado de Santa Catarina, Centro de Ciências Tecnológicas, Programa de Pós-Graduação em Engenharia Elétrica, Joinville, 2025.

1. Dual Active Bridge. 2. Single Phase-Shift. 3. Dual Phase-Shift. 4. Algoritmo. 5. Esforços de Corrente. I. Rômulo de Novaes, Yales. II. Guenter, Sandro. III. Universidade do Estado de Santa Catarina, Centro de Ciências Tecnológicas, Programa de Pós-Graduação em Engenharia Elétrica. IV. Titulo.

# HENRIQUE THOMASELLI TEICHERT

# THE DUAL ACTIVE BRIDGE CONVERTER: A STUDY ON SPS MODULATION AND A CURRENT STRESS REDUCTION ALGORITHM FOR DPS MODULATION

Master's thesis presented to the Graduate Program in Electrical Engineering of the Santa Catarina State University, as requirement for obtention of the title of Master in Electrical Engineering, concentration area of Electronic Systems. Supervisor: Yales Rômulo de Novaes, Dr. Co-supervisor: Sandro Guenter, Dr.

# **EXAMINATION BOARD**

Prof. Yales Rômulo de Novaes, Doctor

State University of Santa Catarina (UDESC-CCT) (Board's president / Supervisor)

Members:

Prof. Sérgio Vidal Garcia Oliveira, Doctor State University of Santa Catarina (UDESC-CCT)

> Chrystian Lenon Remes, Doctor Serasa Experian

# **ACKNOWLEDGMENTS**

I would like to thank Yales Rômulo de Novaes for accepting to be my supervisor, for providing aid when I needed and for sharing with me his knowledge, wisdom and advices throughout my stay during the Master's Program, and also for having the patience to answer my questions and give me the time I needed to finish the work.

I also want to extend my gratitude to Sandro Guenter for accepting to be my cosupervisor and sharing his valuable knowledge, whom offered his time to help us in developing this Master's thesis and made himself available when I needed, despite the challenges of setting meetings while being in a time zone many hours ahead.

I am grateful to my colleague Daniel Gustavo Castellain for offering his fullbridge PCBs, which took him many hours of work, so that I could build my own prototype, saving me a lot of time from designing a power converter.

I am also grateful to my other laboratory colleagues Rodrigo Heinrich, Marcel Maciel Fernandes, Rafael Juliano Scholtz, Luan Souza de Oliveira, Lucas Bona Ruckl, Lucas Zuchi, Felipe Serpa, Paulo Roberto Pereira Junior, Maurício Corrêa Da Silva, Jhon Brajhan Benites Quispe, Filipe Fernandes and Maicon William Machado de Carvalho for lending me their help and for the conversations we had during my time in the laboratory.

To the other professors from the laboratory: Sérgio Vidal Garcia Oliveira, Felipe Joel Zimann, Marcos Vinicius Bressan, Joselito Heerdt, Alessandro Luiz Batschauer and Marcello Mezaroba, for their help, advice and teachings during my Master's thesis journey.

My parents, Evelise Miranda Thomaselli Teichert and José Domingos Teichert, who supported me my whole life and whose support was also necessary during my Master's thesis.

I'm thankful to Plexim for providing student licenses of PLECS to UDESC students. The software was very important for the development of this work.

Lastly, I thank the State University of Santa Catarina and the nPEE for providing the quality education and necessary infrastructure for developing power electronics research, as well as public entities such as CAPES and FAPESC for their essential financial support.

# **ABSTRACT**

The Dual Active Bridge (DAB) is a DC-DC power converter which offers bidirectional power flow, galvanic isolation and natural soft-switching. Such characteristics are interesting for applications like electric vehicles, energy storage systems and DC distribution/transmission grids. In this Master's thesis, an in-depth circuit analysis of the DAB converter employing its simplest modulation (Single Phase-Shift) is done, presenting steady-state waveforms, deriving equations of important parameters for converter design and explaining concepts like circulating power and soft-switching. A 600 W prototype is built for experimental validation of the mathematical model. Furthermore, an automatic algorithm for the Dual Phase-Shift modulation named mCSPT is proposed for reducing the current stress in the transformer and the power switches. The algorithm is validated by both simulation and experimental results.

**Keywords:** Dual Active Bridge; Single Phase-Shift; Dual Phase-Shift; Algorithm; Current Stress.

# **RESUMO**

O Dual Active Bridge (DAB) é um conversor estático CC-CC que oferece fluxo de potência bidirecional, isolação galvânica e comutação suave natural. Tais características são interessantes para aplicações como veículos elétricos, sistemas de armazenamento de energia e redes CC de distribuição/transmissão de energia elétrica. Nesta dissertação, uma profunda análise da topologia é feita do conversor DAB empregando sua modulação mais simples (Single Phase-Shift), apresentando formas de onda em regime permanente, deduzindo equações de importantes parâmetros para projeto do conversor e explicando conceitos como potência circulante e comutação suave. Um protótipo de 600 W é construído para validar experimentalmente a teoria. Além disso, um algoritmo automático para a modulação Dual Phase-Shift nomeado de mCSPT é proposto para reduzir os esforços de corrente no transformador e nos interruptores de potência. O algoritmo é validado tanto por resultados de simulação quanto experimentais.

**Palavras-chave:** *Dual Active Bridge*; *Single Phase-Shift*, *Dual Phase-Shift*, Algoritmo; Esforços de Corrente.

# **LIST OF FIGURES**

| Figure 1 – Topology diagram for the conventional DAB                                         | 23 |

|----------------------------------------------------------------------------------------------|----|

| Figure 2 – Definitions used for the DAB converter topology                                   | 40 |

| Figure 3 – Voltages and currents defined for analyzing the DAB                               | 41 |

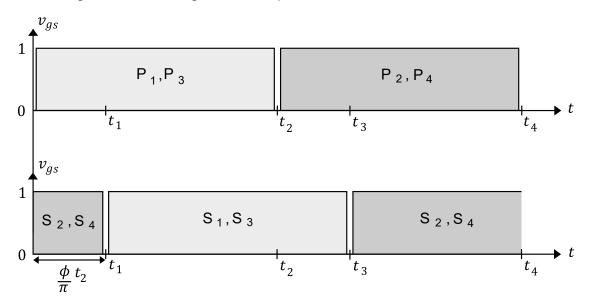

| Figure 4 – Gate signals of the power switches in SPS modulation                              | 42 |

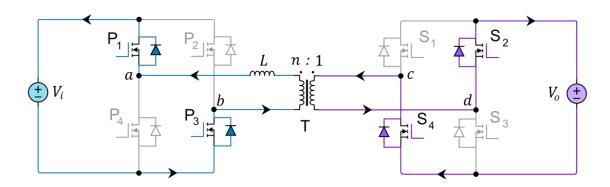

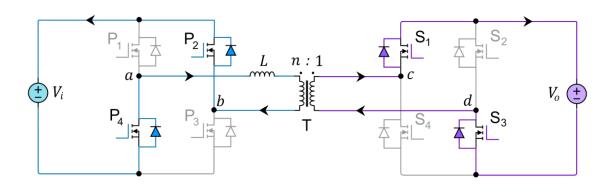

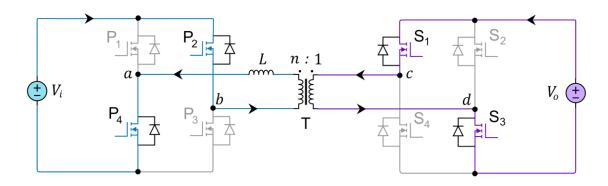

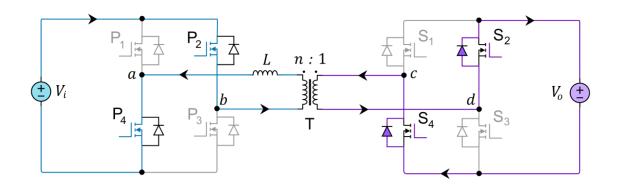

| Figure 5 – Stage 1 of a DAB converter operating in SPS                                       | 43 |

| Figure 6 – Stage 2 of a DAB converter operating in SPS                                       | 43 |

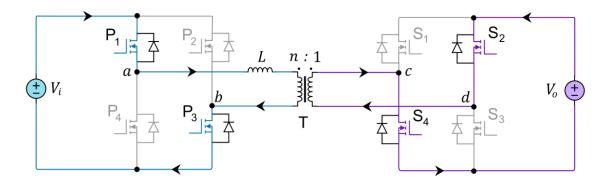

| Figure 7 – Stage 3 of a DAB converter operating in SPS                                       | 44 |

| Figure 8 – Stage 4 of a DAB converter operating in SPS                                       | 44 |

| Figure 9 – Stage 5 of a DAB converter operating in SPS                                       | 45 |

| Figure 10 – Stage 6 of a DAB converter operating in SPS                                      | 45 |

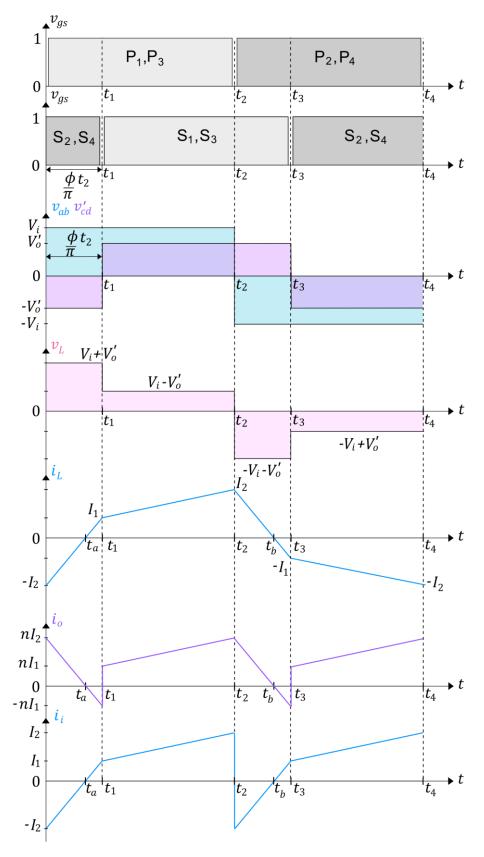

| Figure 11 – Main voltages and currents waveforms of the DAB converter operating              | in |

| buck mode with SPS modulation                                                                | 47 |

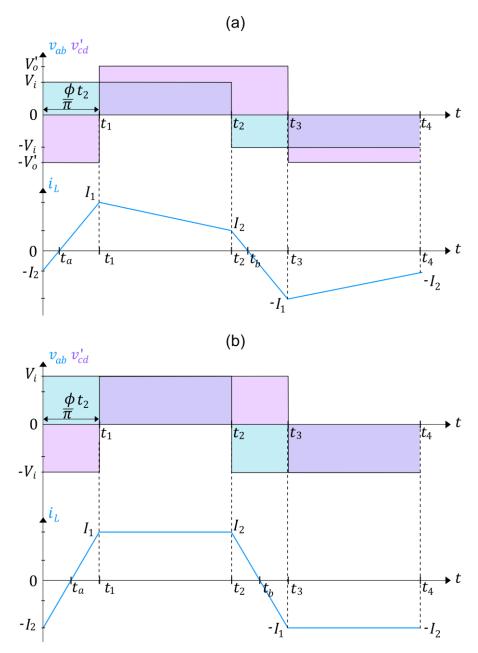

| Figure 12 – Inductor current for other modes of operation. (a) Boost mode and (b)            |    |

| Voltage Match mode                                                                           | 48 |

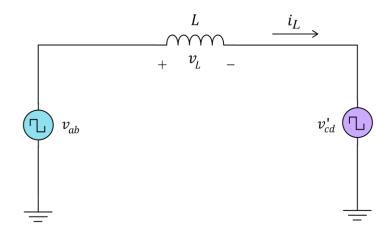

| Figure 13 – Equivalent circuit for power transfer in the lossless DAB converter              | 49 |

| Figure 14 – Inductor current waveform highlighting the switching currents                    | 51 |

| Figure 15 – Power Transmission versus Phase-Shift plot of DAB converter using S              | PS |

| modulation                                                                                   | 53 |

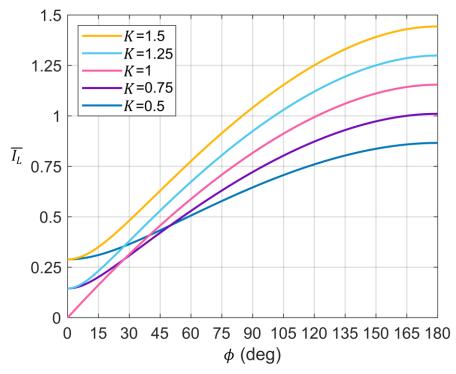

| Figure 16 – Normalized RMS value of $iL$ versus $\phi$ plot                                  | 56 |

| Figure 17 – Normalized RMS value of $iL$ versus $\phi$ plot for different values of $K$      | 56 |

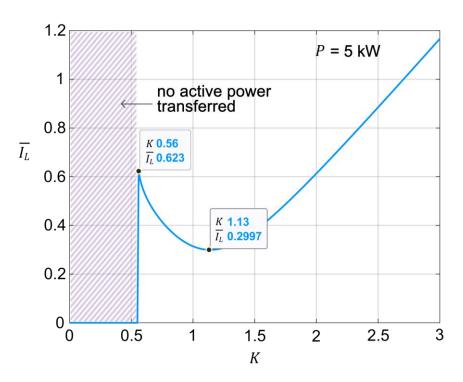

| Figure 18 – Plot of IL versus K for $P=5\ kW$ . Parameters of the converter are: $Vi=1$      | =  |

| $100 \ V, n = 1, L = 13.88 \ \mu H \text{ and } fs = 10 \ kHz.$                              | 57 |

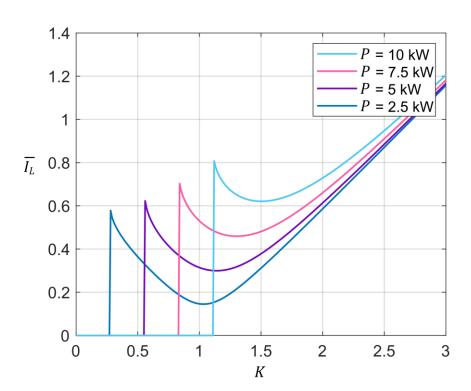

| Figure 19 – Plot of $IL$ versus $K$ for different values of $P$ . Parameters of the converte | r  |

| are: $Vi = 100 V$ , $n = 1$ , $L = 13.88 \mu H$ and $fs = 10 kHz$                            | 58 |

| Figure 20 – Circulating power generation, waveforms for $iL0 < 0$ and $iLt1 > 0$ , fo        | r  |

| buck mode                                                                                    | 60 |

| Figure 21 – Circulating power generation, waveforms for $iL0 > 0$ and $iLt1 > 0$ , in        | 1  |

| boost mode                                                                                   | 62 |

| Figure 22– Circulating power generation for voltage match mode                               | 64 |

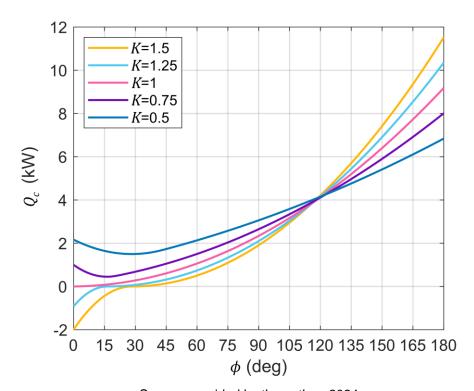

| Figure 23 – | - Circulating power plot versus phase-shift, for different values of K.             |

|-------------|-------------------------------------------------------------------------------------|

|             | Parameters of the converter are: $Vi=100~V, n=1, L=13.88~\mu H$ and                 |

|             | fs = 10  kHz. 65                                                                    |

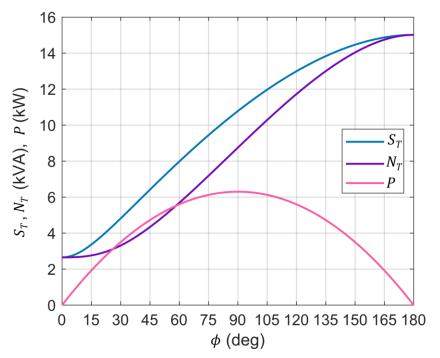

| Figure 24 - | Power plot of the transformer as function of $\phi$ , for $Vo = 70 V$ ( $K =$       |

|             | 0.7). $Vi = 100  V$ , $n = 1$ , $L = 13.88  \mu H$ and $fs = 10  kHz$ 67            |

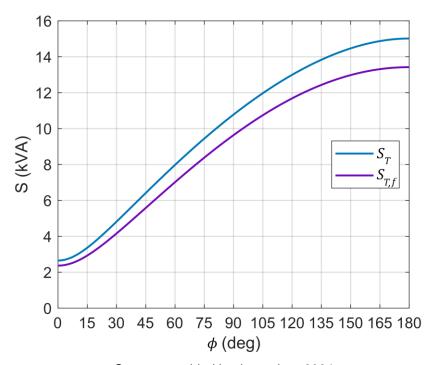

| Figure 25 – | Comparison of Transformer VA rating equations, for $K = 0.7$ . $Vi = 0.7$           |

|             | $100 \ V, n = 1, L = 13.88 \ \mu H \text{ and } fs = 10 \ kHz.$ 67                  |

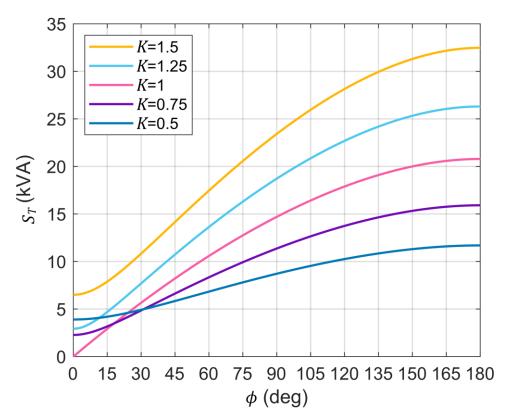

| Figure 26 – | Transformer power rating $ST$ as function of $\phi$ , for different values of $K$ . |

|             | Parameters of the converter are: $Vi=100V$ , $n=1$ , $L=13.88\mu H$ and             |

|             | fs = 10  kHz.                                                                       |

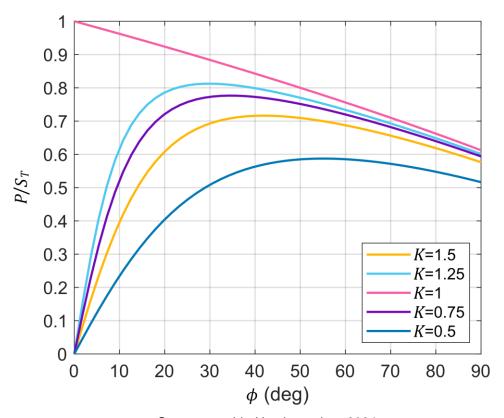

| Figure 27 – | Transformer utilization factor as function of $\phi$ for different values of $K$ .  |

|             | Parameters of the converter are: $Vi=100~V, n=1, L=13.88~\mu H$ , and               |

|             | fs = 10  kHz.                                                                       |

| Figure 28 – | - Current waveforms in the semiconductors for buck mode, $iL0 < 0$ and              |

|             | iLt1 > 0, for buck mode71                                                           |

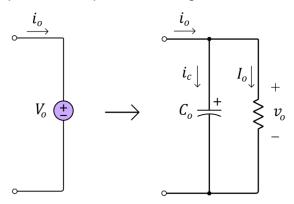

| Figure 29 – | - Equivalent output circuit stage for a resistive load                              |

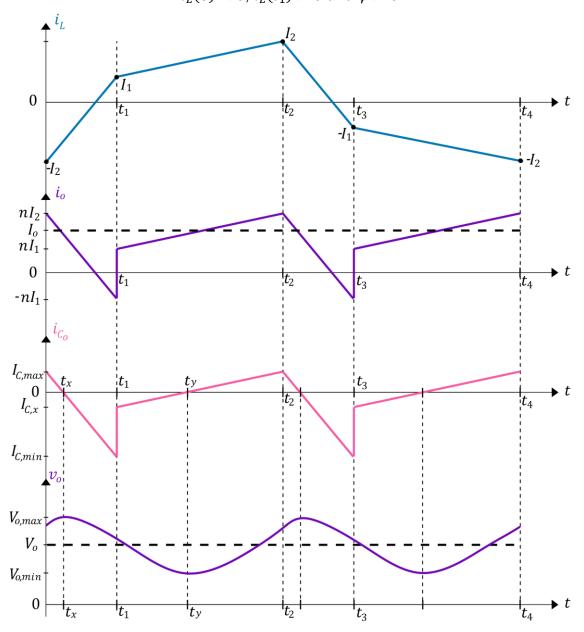

| Figure 30 – | Capacitor $Co$ current and voltage waveforms for buck mode, $iL0 < 0$ ,             |

|             | $iLt1>0$ and $\phi>0$ 76                                                            |

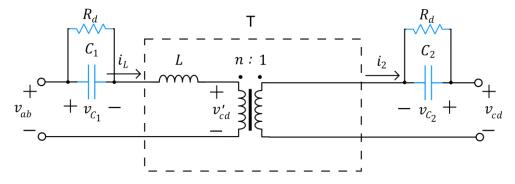

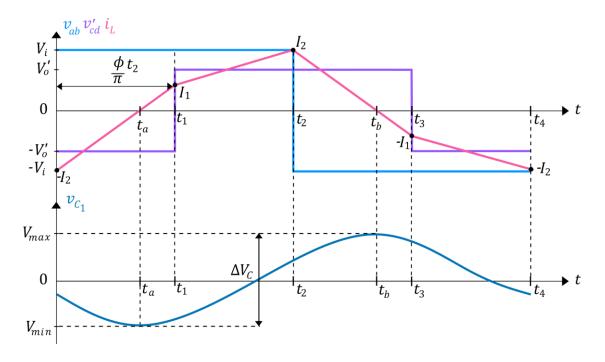

| Figure 31 – | Diagram of transformer with series DC blocking capacitors78                         |

| Figure 32 – | Voltage and current waveforms in DC blocking series capacitor C180                  |

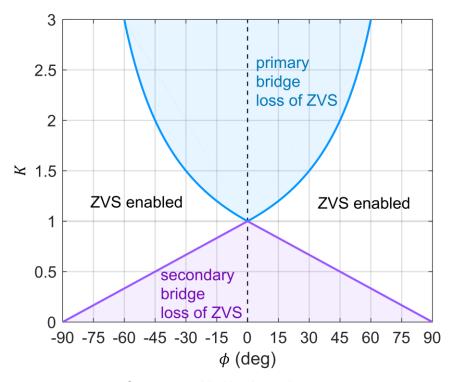

| Figure 33 – | Plot of $K$ versus $\phi$ with ZVS regions considering ideal switches84             |

| Figure 34 - | Plot of $P$ versus $\phi$ with ZVS regions considering ideal switches86             |

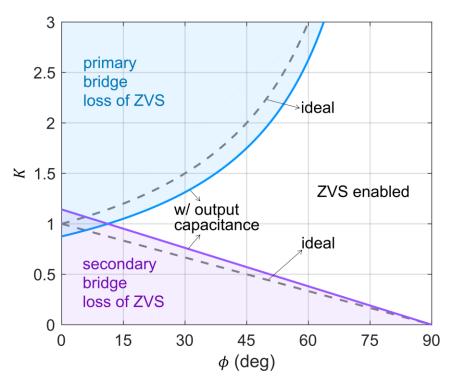

| Figure 35 – | DAB converter diagram with the switches' output capacitances86                      |

| Figure 36 - | Plot of $K$ versus $\phi$ with ZVS regions considering the switches' output         |

|             | capacitance. Parameters: $L=13.88~\mu H, n=1, fs=10~kHz$ and                        |

|             | CP = CS = 350  nF.                                                                  |

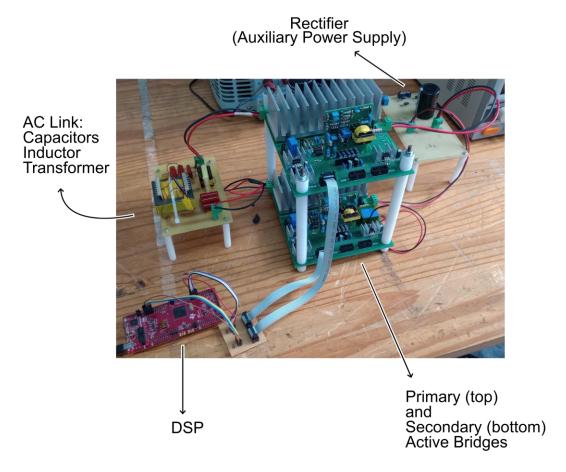

| Figure 37 – | Picture of the Active Bridge board used for the prototype94                         |

| Figure 38 – | Picture of the inductor (above pen) and transformer (below pen) built for           |

|             | the prototype99                                                                     |

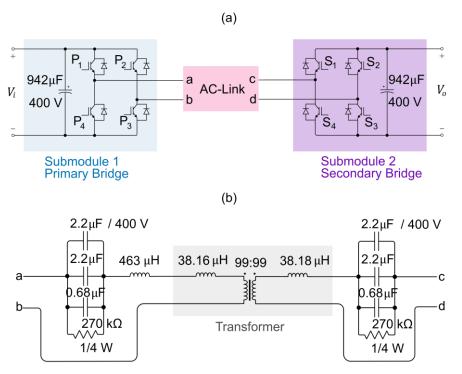

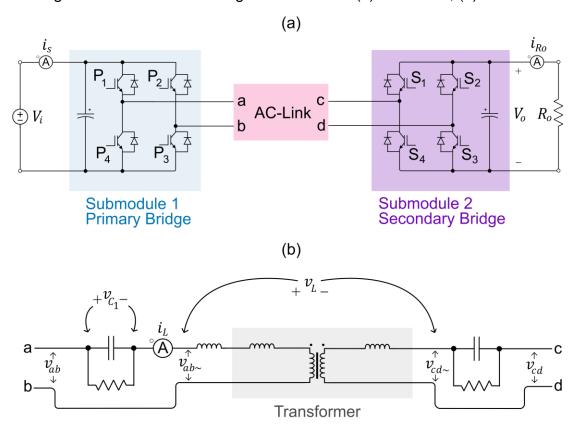

| Figure 39 – | Prototype circuit diagram: (a) power converter (b) AC-Link107                       |

| Figure 40 – | - DSP LAUNCHXL-F28379D board from Texas Instruments108                              |

| Figure 41 – | - Assembled DAB prototype and its components                                        |

| Figure 42 – | Setup for experimental tests with prototype for SPS modulation109                   |

|             |                                                                                     |

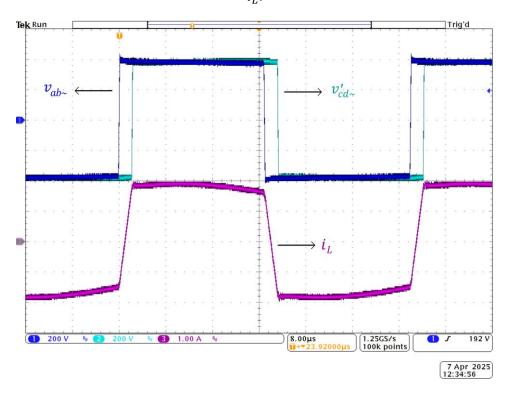

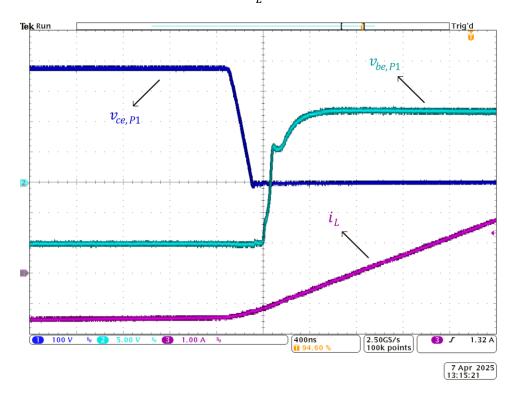

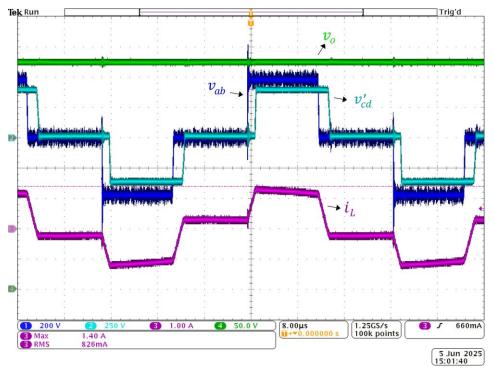

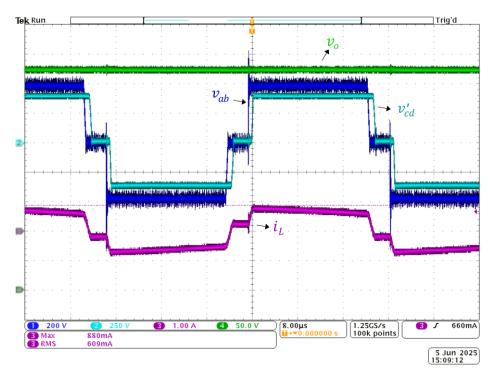

| Figure 43 – Measured voltages and current: (a) Converter, (b) AC-Link110                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 44 – Experimental waveform results of SPS modulation: $vab$ , $vcd$ and $iL$ 112                                                            |

| Figure 45 - Experimental waveform results of SPS modulation: $vab\sim$ , $vcd\sim$ and $iL$ .                                                      |

| 112                                                                                                                                                |

| Figure 46 - Experimental waveform results of SPS modulation: $\emph{vL}$ and $\emph{iL}$ 113                                                       |

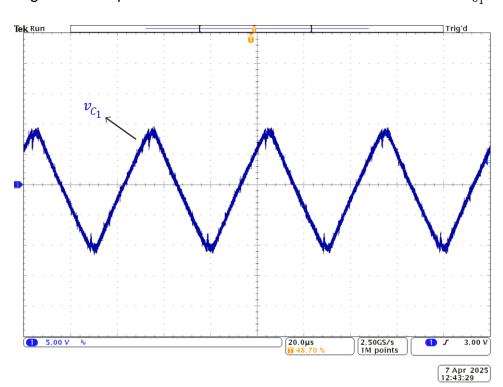

| Figure 47 - Experimental waveform results of SPS modulation: $\emph{vC}1$ 113                                                                      |

| Figure 48 - Experimental waveform results of SPS modulation: $\emph{vo}$ and $\emph{iRo}$ 114                                                      |

| Figure 49 - Experimental waveform results of SPS modulation: $vce, P1, vbe, P1$ and                                                                |

| <i>iL</i> 114                                                                                                                                      |

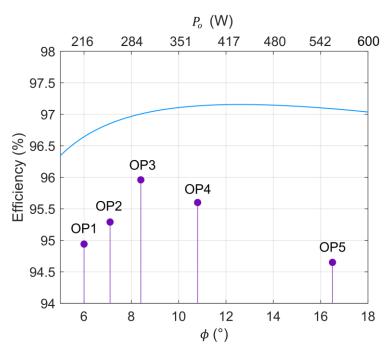

| Figure 50 – Plot of Efficiency estimative (continuous line) and experimental results                                                               |

| (dots) for the prototype operating with SPS modulation120                                                                                          |

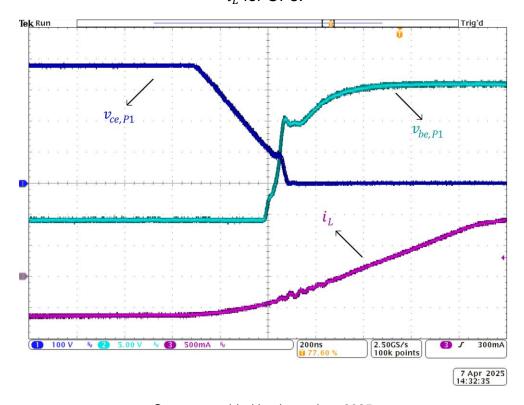

| Figure 51 - Experimental waveform results of SPS modulation: $\textit{vce}, \textit{P1}, \textit{vbe}, \textit{P1}$ and $\textit{iL}$              |

| for OP3121                                                                                                                                         |

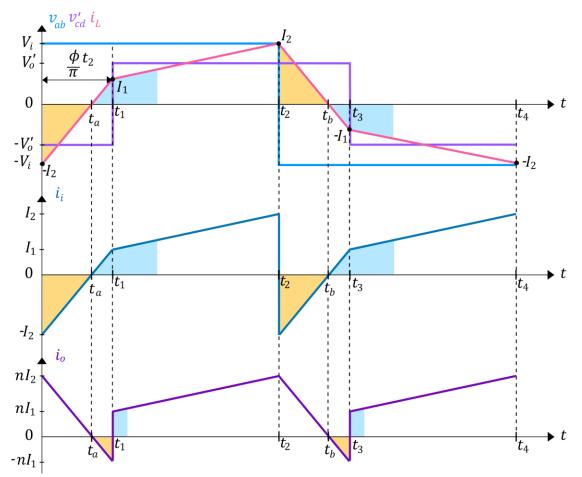

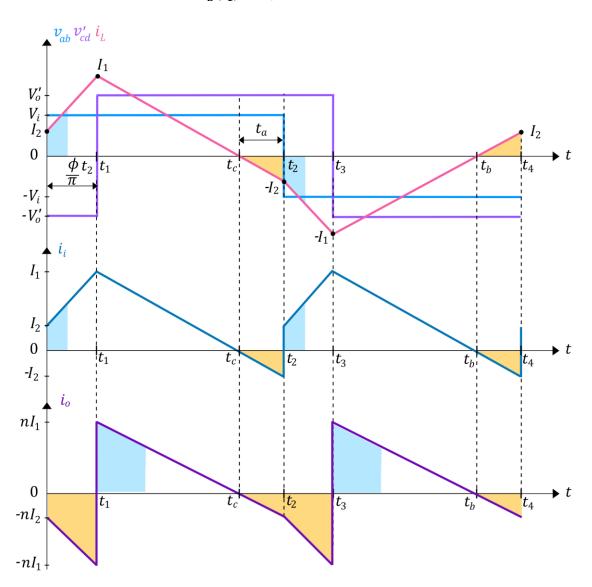

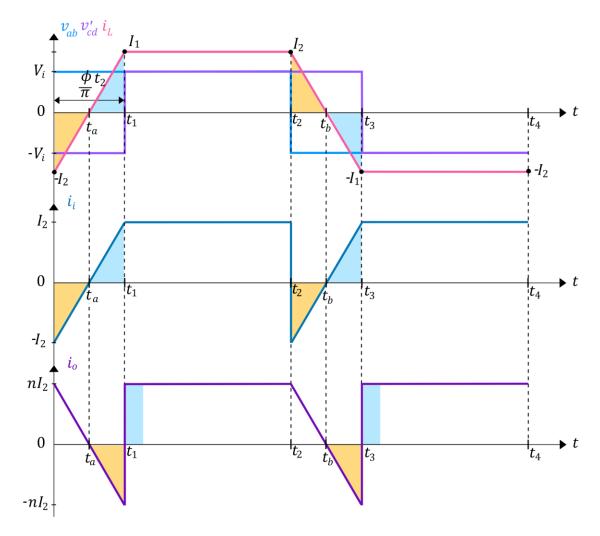

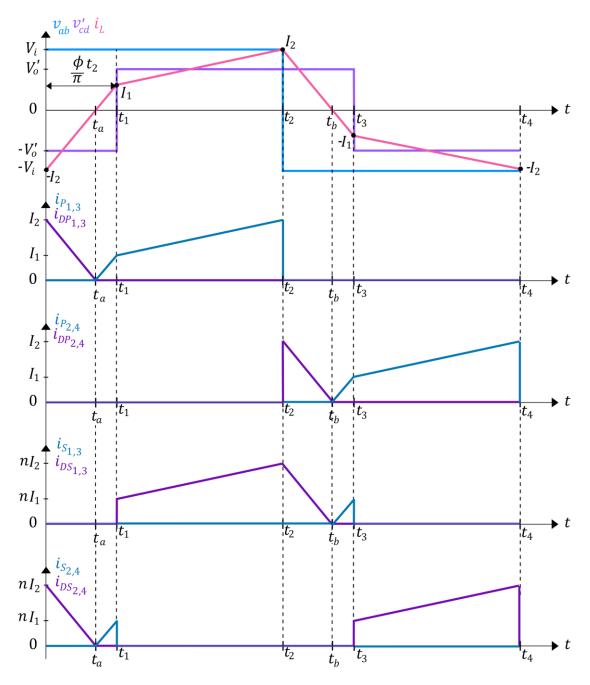

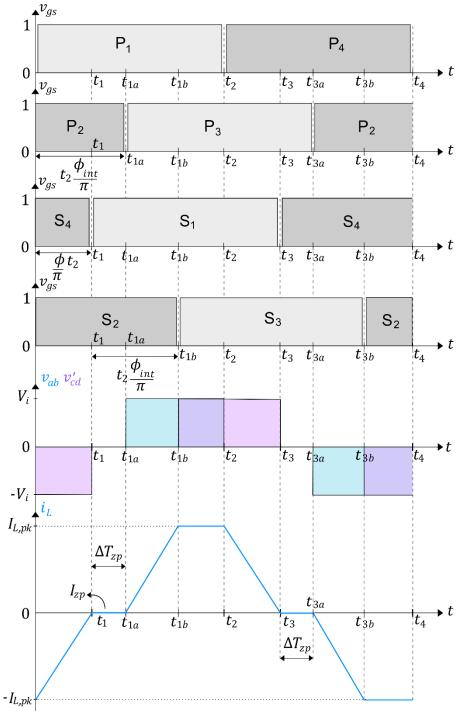

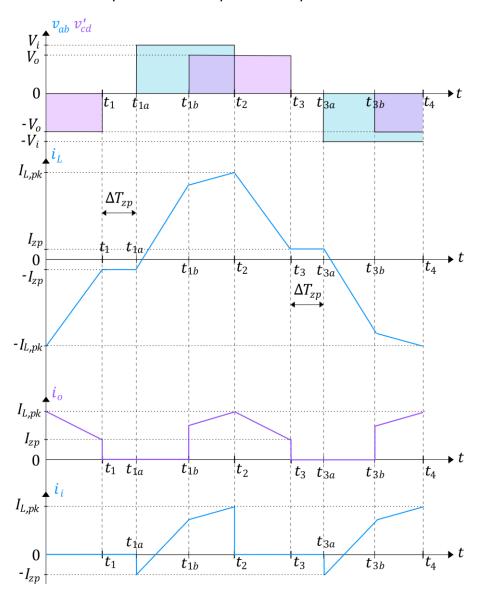

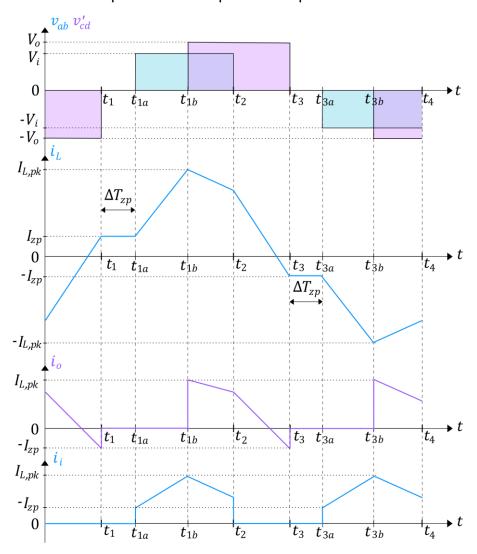

| Figure 52 – Main waveforms for DPS modulation operating in Voltage Match mode                                                                      |

| and $\phi int > \phi \wedge \phi int < 90^{\circ} \wedge \phi < 90^{\circ}$ 124                                                                    |

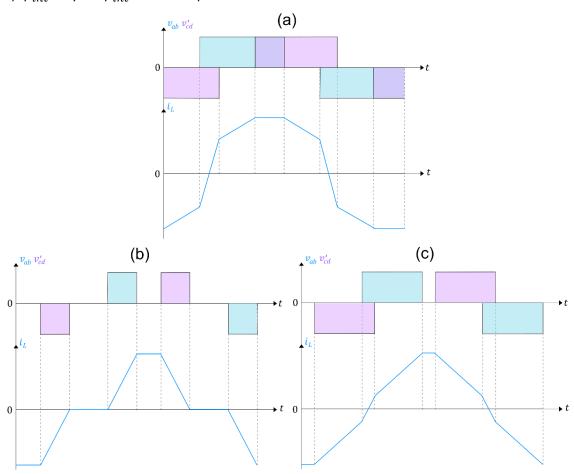

| Figure 53 – Different <i>iL</i> shapes for other conditions in Voltage Match mode: a)                                                              |

| $\phi int < \phi \land \phi int < 90^{\circ} \land \phi < 90^{\circ}$ ; b) $\phi int > \phi \land \phi int > 90^{\circ} \land \phi < 90^{\circ}$ ; |

| c) $\phi int < \phi \land \phi int < 90^{\circ} \land \phi > 90^{\circ}$ 125                                                                       |

| Figure 54 – Normalized power transmitted plot versus $\phi$ and $\phi int$ for DPS                                                                 |

| modulation126                                                                                                                                      |

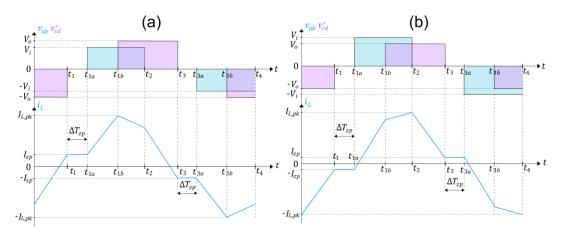

| Figure 55 - $vab$ , $v'cd$ and $iL$ waveforms in DPS modulation when $\phi int > \phi \wedge \phi int < \phi$                                      |

| $90^{\circ} \wedge \phi < 90^{\circ}$ for: a) Boost mode; b) Buck mode127                                                                          |

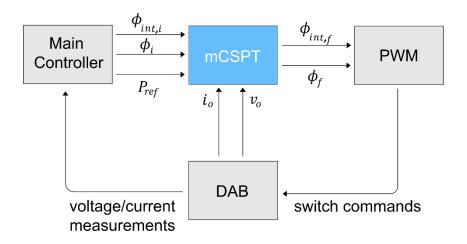

| Figure 56 – Block diagram of a control system using the mCSPT algorithm131                                                                         |

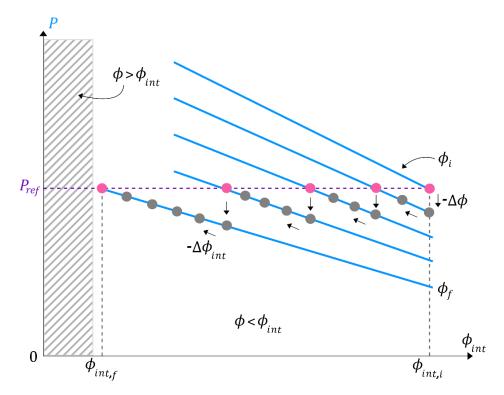

| Figure 57 – Plot of $P$ versus $\phi int$ and $\phi$ , illustrating the operation of the mCSPT                                                     |

| algorithm132                                                                                                                                       |

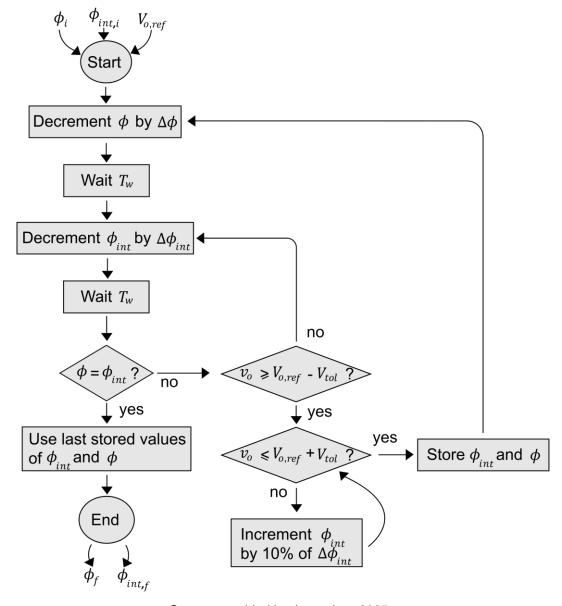

| Figure 58 – Flowchart diagram of the mCSPT algorithm operation134                                                                                  |

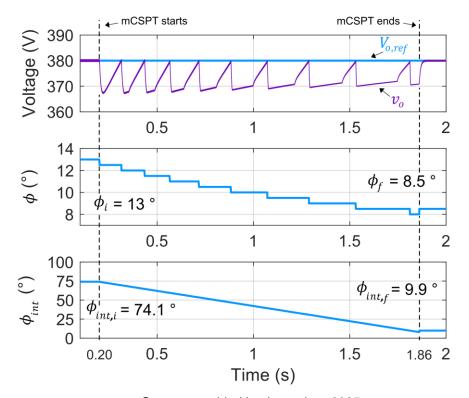

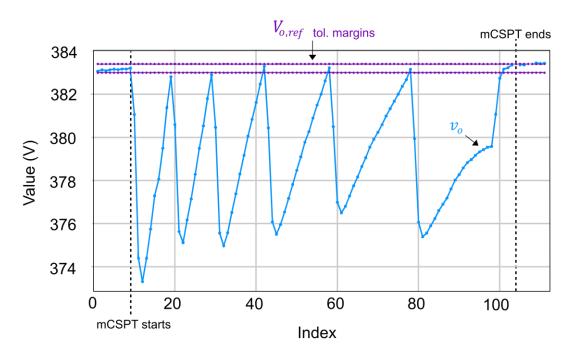

| Figure 59 – Simulation results of mCSPT execution: output and reference voltage                                                                    |

| (top), external (middle) and internal (bottom) phase-shift136                                                                                      |

| Figure 60 - Simulation results of mCSPT execution: RMS (top) and peak (bottom)                                                                     |

| values of transformer current137                                                                                                                   |

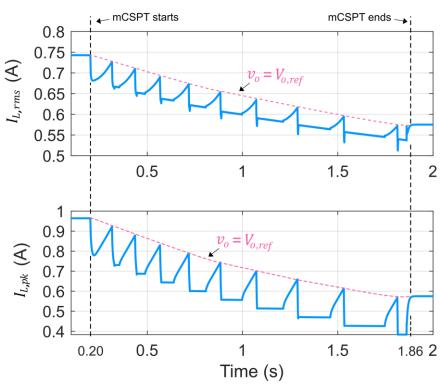

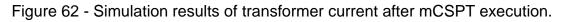

| Figure 61 - Simulation results of transformer current before mCSPT execution138                                                                    |

| Figure 62 - Simulation results of transformer current after mCSPT execution138                                                                     |

| Figure 63 – Hardware setup diagram for mCSPT experimental test                                                                                     |

| Figure 64 – | Flowchart diagram of interruption routines implemented in the DSP fo             | r   |

|-------------|----------------------------------------------------------------------------------|-----|

|             | mCSPT testing                                                                    | 140 |

| Figure 65 – | Pseudocode of the mCSPT algorithm implemented in the DSP for                     |     |

|             | experimental test.                                                               | 141 |

| Figure 66 – | Picture of hardware setup for experimental test of mCSPT                         | 142 |

| Figure 67 – | Main experimental voltages and current waveforms of DAB operating                |     |

|             | before mCSPT execution.                                                          | 143 |

| Figure 68 – | Output voltage measured by the DSP seen in Code Composer Studio                  | 1   |

|             | software during mCSPT execution.                                                 | 143 |

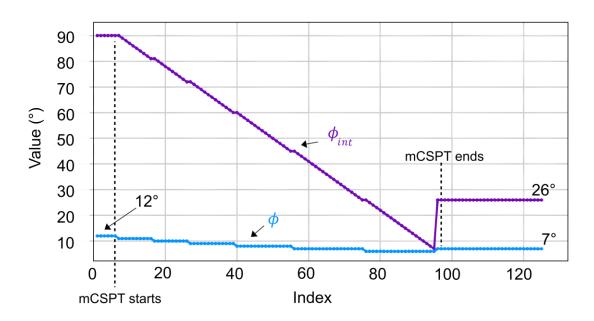

| Figure 69 – | External (blue) and internal (purple) phase-shifts used by the DSP see           | en  |

|             | in Code Composer Studio software during mCSPT execution                          | 144 |

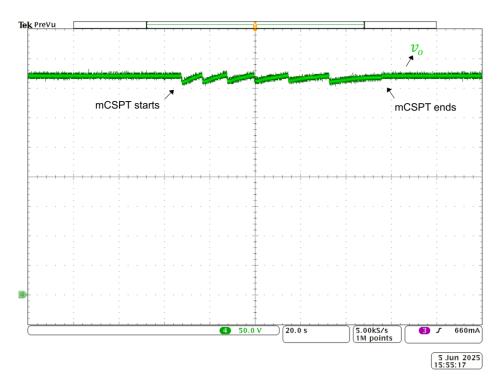

| Figure 70 – | Experimental output voltage waveform of the converter during mCSP                | Γ   |

|             | execution.                                                                       | 145 |

| Figure 71 - | Main experimental voltages and current waveforms of DAB operating                |     |

|             | after mCSPT execution.                                                           | 145 |

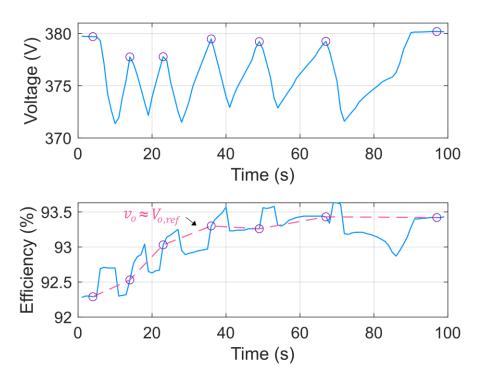

| Figure 72 – | Experimental measurement by power analyzer of output voltage (top)               |     |

|             | and efficiency (bottom) of converter during mCSPT execution                      | 146 |

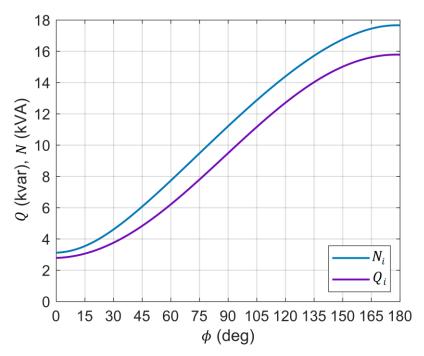

| Figure 73 – | Plot of $Qi$ and $Ni$ versus $\phi$ for $K=0.7$ . Parameters of the converter as | re: |

|             | $Vi=100~V, n=1, L=13.88~\mu H$ and $fs=10~kHz.$                                  | 161 |

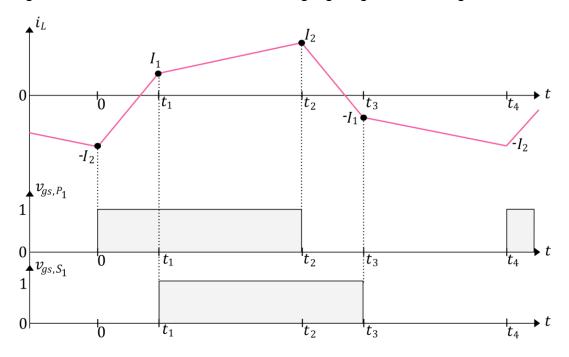

| Figure 74 – | DPS modulation waveforms for $\phi < \phi int$ during buck mode operation        | l   |

|             | with input and output currents                                                   | 170 |

| Figure 75 - | DPS modulation waveforms for $\phi < \phi int$ during boost mode operation       | 1   |

|             | with input and output currents                                                   | 171 |

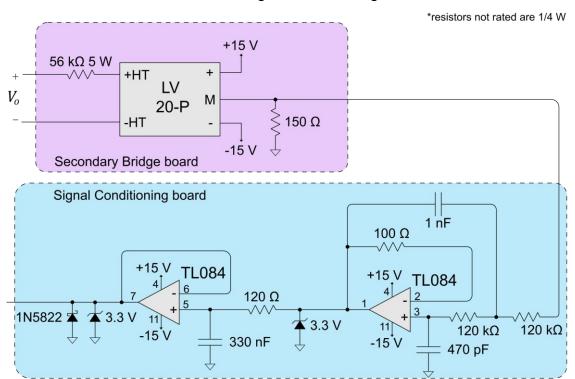

| Figure 76 – | Circuit schematic of output voltage sensor and signal conditioning boa           | ard |

|             | for testing the mCSPT algorithm.                                                 | 173 |

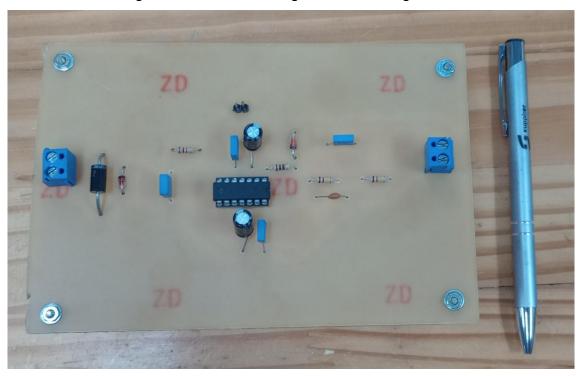

| Figure 77 – | Picture of signal conditioning board                                             | 174 |

| Figure 78 – | Schematic diagram of DSP connections                                             | 175 |

|             |                                                                                  |     |

# **LIST OF TABLES**

| Table 1 – Traditional Phase-Shift modulations comparison                       | 30  |

|--------------------------------------------------------------------------------|-----|

| Table 2 – High power DAB prototypes reported in the literature                 | 39  |

| Table 3 – Instant time values for $\phi>0.$                                    | 42  |

| Table 4 – Converter parameters for the DAB prototype                           | 93  |

| Table 5 – Specifications of Primary and Secondary Bridges for the prototype    | 93  |

| Table 6 – Main parameters of the IGBT APT15GT60BRDQ1                           | 94  |

| Table 7 – Thornton ferrite core used for transformer                           | 97  |

| Table 8 – Transformer construction parameters                                  | 97  |

| Table 9 – Measurements from built transformer with LCR Meter (at 10 kHz        |     |

| frequency)                                                                     | 98  |

| Table 10 – Additional inductor specifications                                  | 99  |

| Table 11 – Semiconductors current stresses for the prototype                   | 101 |

| Table 12 - Operation points for measurements acquisitions                      | 110 |

| Table 13 – Actual phase-shift values used for each operation point             | 115 |

| Table 14 – Experimental results of input current and input power               | 116 |

| Table 15 – Experimental results of current and voltages on the transformer     | 116 |

| Table 16 - Experimental results of the switching currents                      | 117 |

| Table 17 – Experimental results of the transformer apparent power              | 117 |

| Table 18 – Experimental results of output current and power                    | 118 |

| Table 19 – Experimental results of DC blocking capacitor voltage               | 118 |

| Table 20 – Experimental results of the temperature in the magnetic cores       | 119 |

| Table 21 – Efficiency estimates and measurements from each operation point     | 120 |

| Table 22 – Simulation results in Voltage Match mode for investigation of DPS   |     |

| modulation                                                                     | 128 |

| Table 23 - Simulation results in Buck and Boost modes for investigation of DPS |     |

| modulation                                                                     | 129 |

| Table 24 – mCSPT parameters for experimental test                              | 140 |

| Table 25 – Experimental measurements of RMS and peak values of transformer     |     |

| current before and after mCSPT execution                                       | 146 |

| Table 26 – Semiconductors current stresses for negative power flow operation   | 163 |

| Table 27 – Equipment used for the experimental tests.                          | 169 |

# LIST OF ABBREVIATIONS AND ACRONYMS

NASA National Aeronautics and Space Administration

IPCC Intergovernmental Panel on Climate Change

CO<sub>2</sub> Carbon Dioxide

IEA International Energy Agency

EIA United States Energy Information Administration

BESS Battery Energy Storage System

IRENA International Renewable Energy Agency

EV Electric Vehicles

V2G Vehicle to Grid

DC Direct Current

AC Alternate Current

DAB Dual Active Bridge

PWM Pulse Width Modulation

ZVS Zero Voltage Switching

MEA More Electric Aircrafts

SST Solid State Transformer

RMS Root Mean Square

SPS Single Phase-Shift

EPS Extended Phase-Shift

DPS Dual Phase-Shift

TPS Triple Phase-Shift

PS Phase-Shift

LV Low Voltage

MV Medium Voltage

HV High Voltage

NPC Neutral Point Clamped

ISOP Input Series Output Parallel

MOSFET Metal Oxide Semiconductor Field Effect Transistor

5LDAB 5 (Five) Level Dual Active Bridge

DSP Digital Signal Processor

ANPC Active Neutral Point Clamped

Si Sillicon

SiC Sillicon Carbide

GaN Gallium Nitride

FPGA Field Programmable Gate Array

IGBT Insulated Gate Bipolar Transistor

PFC Power Factor Correction

G2V Grid to Vehicle

ZCS Zero Current Switching

PCB Printed Circuit Board

mCSPT Minimum Current Stress Point Tracking

ADC Analog-to-Digital Converter

IIR Infinite Impulse Response

# LIST OF SYMBOLS

| $V_i$     | Input Voltage [V]                                                     |

|-----------|-----------------------------------------------------------------------|

| $V_o$     | Output Voltage [V]                                                    |

| n         | Transformer Turns Ratio                                               |

| K         | Voltage Conversion Ratio                                              |

| L         | Inductance [H]                                                        |

| $C_i$     | Input Capacitance [F]                                                 |

| $C_o$     | Output Capacitance [F]                                                |

| T         | Transformer                                                           |

| Px        | Power Switch "x" of the Primary Bridge                                |

| $S_{x}$   | Power Switch "x" of the Secondary Bridge                              |

| $\phi$    | External Phase-Shift [rad]                                            |

| $N_1$     | Number of Turns on the Primary Side of the Transformer                |

| $N_2$     | Number of Turns on the Secondary Side of the Transformer              |

| $v_{ab}$  | Output Voltage of Primary Bridge [V]                                  |

| $v_{cd}$  | Output Voltage of Secondary Bridge [V]                                |

| $v_{cd}'$ | Output Voltage of Secondary Bridge Referred to the Primary [V]        |

| $i_i$     | Input Current [A]                                                     |

| $i_L$     | Inductor Current [A]                                                  |

| $i_o$     | Output Current [A]                                                    |

| $T_{S}$   | Switching Period [s]                                                  |

| t         | Time [s]                                                              |

| $t_x$     | Time Instant "x" [s]                                                  |

| $V_o'$    | Output Voltage Referred to the Primary [V]                            |

| $i_1$     | Primary Side Transformer Current [A]                                  |

| $i_2$     | Secondary Side Transformer Current [A]                                |

| $arphi_i$ | Phase Angle of the Input Voltage Source [°]                           |

| $arphi_o$ | Phase Angle of the Output Voltage Source [°]                          |

| $P_i$     | Input Power [W]                                                       |

| $P_o$     | Output Power [W]                                                      |

| $I_1$     | Switching Current 1 (value of inductor current at instant $t_1$ ) [A] |

| $I_2$     | Switching Current 2 (value of inductor current at instant $t_2$ ) [A] |

|           |                                                                       |

$f_s$  Switching Frequency [Hz]

P Power Transmission [W]

*P<sub>b</sub>* Base Value of Power Transmission [W]

$\bar{P}$  Normalized Power Transmission [p.u.]

$I_{2,rms}$  RMS Value of Secondary Side Transformer Current [A]

$I_{L,rms}$  RMS Value of the Inductor Current [A]

$I_{L,b}$  Base Value of RMS Value of the Inductor Current [A]

$\overline{I_L}$  Normalized RMS Value of the Inductor Current [p.u.]

$I_i$  Average Value of the Input Current [A]

$I_{i,rms}$  RMS Value of the Input Current [A]

*I*<sub>o</sub> Average Value of the Output Current [A]

$I_{o.rms}$  RMS Value of the Output Current [A]

*Q<sub>c</sub>* Circulating Power [W]

*V<sub>ab.rms</sub>* RMS Value of Voltage Between Nodes "a" and "b" [V]

$I_{ab.rms}$  RMS Value of Current Between Nodes "a" and "b" [A]

$Q_T$  Transformer Reactive Power [var]

$D_T$  Transformer Distortion Power [VA]

$N_T$  Transformer Non-Active Power [VA]

$S_T$  Transformer Apparent Power [VA]

$S_{T.f}$  Transformer Apparent Power by Fundamental Component [VA]

*I<sub>P</sub>* Average Value of Current in Unidirectional Switch "P" [A]

$I_{DP}$  Average Value of Current in Diode of Power Switch "P" [A]

I<sub>S</sub> Average Value of Current in Unidirectional Switch "S" [A]

$I_{DS}$  Average Value of Current in Diode of Power Switch "S" [A]

*I<sub>P.rms</sub>* RMS Value of Current in Unidirectional Switch "P" [A]

$I_{DP,rms}$  RMS Value of Current in Diode of Power Switch "P" [A]

*I<sub>S,rms</sub>* RMS Value of Current in Unidirectional Switch "S" [A]

*I<sub>DS.rms</sub>* RMS Value of Current in Diode of Power Switch "S" [A]

$P_R$  Rated Power [W]

$\phi_R$  Rated Phase-Shift [rad]

$v_c$  Capacitor Voltage [V]

*i<sub>C</sub>* Capacitor Current [A]

*i*<sub>Co</sub> Output Capacitor Current [A]

$\Delta V_o$  Output Voltage Ripple [V]

$I_{C_0,rms}$  RMS Value of Output Capacitor Current [A]

$C_1$  Series Capacitance in the Primary Bridge [F]

C<sub>2</sub> Series Capacitance in the Secondary Bridge [F]

$v_{C_1}$  Voltage of the Capacitor  $C_1$  [V]

$v_{C_2}$  Voltage of the Capacitor  $C_2$  [V]

$f_{LC}$  Resonant Frequency [Hz]

C Capacitance [F]

$V_{max}$  Maximum/Peak Voltage [V]

$V_{min}$  Minimum Voltage [V]

$\Delta V_C$  Voltage Ripple in the Series Capacitor  $C_1$  [V]

$V_{max,C_1}$  Maximum Voltage of the Capacitor  $C_1$  [V]

$V_{max,C_2}$  Maximum Voltage of the Capacitor  $C_2$  [V]

$\phi_a$  Applied External Phase-Shift Angle [rad]

$\phi_{dt}$  External Phase-Shift Angle for Compensating Dead-time [rad]

$\phi_{db}$  Full Dead-time Phase-Shift Angle [rad]

$T_{dt}$  Dead-time Period [s]

$\overline{I_1}$  Normalized Switching Current  $I_1$  [p.u.]  $\overline{I_2}$  Normalized Switching Current  $I_2$  [p.u.]

$K_{PR}$  Boundary Value of K for ZVS Region in the Primary Bridge

$K_{SR}$  Boundary Value of K for ZVS Region in the Secondary Bridge

$\bar{P}_{PB}$  Normalized Power Transmission Boundary Value of ZVS Region in

the Primary Bridge [p.u.]

$\bar{P}_{SB}$  Normalized Power Transmission Boundary Value of ZVS Region in

the Secondary Bridge [p.u.]

$I_{ZVS}$  Minimum Inductor Current Value at Switching Instant Necessary for

ZVS [A]

*V<sub>O</sub>* Voltage Over Power Switch [V]

m Number of Turned-On Power Switches

C<sub>P</sub> Output Capacitance of Power Switch in the Primary Bridge [F]

$C_S$  Output Capacitance of Power Switch in the Secondary Bridge [F]

| $I_{ZVS,P}$    | Minimum Inductor Current Value at Switching Instant Necessary for    |

|----------------|----------------------------------------------------------------------|

|                | ZVS in the Primary Bridge [A]                                        |

| $I_{ZVS,S}$    | Minimum Inductor Current Value at Switching Instant Necessary for    |

|                | ZVS in the Secondary Bridge [A]                                      |

| $t_{ZVS,P}$    | Minimum Dead-Time Necessary for ZVS in the Primary Bridge [s]        |

| $t_{ZVS,S}$    | Minimum Dead-Time Necessary for ZVS in the Secondary Bridge [s]      |

| $Q_{C_P}$      | Charge of Capacitor $C_P$ [C]                                        |

| $Q_{C_S}$      | Charge of Capacitor $C_S$ [C]                                        |

| $L_M$          | Magnetizing Inductance [H]                                           |

| $L_{dab}$      | External/Discrete Inductance [H]                                     |

| $l_1$          | Transformer Leakage Inductance on the Primary Side [H]               |

| $l_2$          | Transformer Leakage Inductance on the Secondary Side [H]             |

| $l_2'$         | Secondary Side Leakage Inductance Referred to Primary [H]            |

| $t_f$          | Power Switch Current Fall Time [s]                                   |

| $P_{sw,off}$   | Turn Off Switching Loss [W]                                          |

| $V_{f,igbt}$   | Estimated Voltage Drop of Collector-Emitter Channel of IGBT [V]      |

| $R_{ce,igbt}$  | Estimated Resistance of Collector-Emitter Channel of IGBT $[\Omega]$ |

| $P_{on,ce}$    | Conduction Loss of Collector-Emitter Channel of IGBT [W]             |

| $V_{f,D}$      | Estimated Forward Voltage of Diode [V]                               |

| $R_D$          | Estimated Resistance of Diode $[\Omega]$                             |

| $P_{on,D}$     | Conduction Loss of Diode [W]                                         |

| $T_j$          | Junction Temperature [°C]                                            |

| $T_a$          | Ambient Temperature [°C]                                             |

| $R_{cd}$       | Thermal Resistance of Case-to-Heatsink [°C/W]                        |

| $R_{jc}$       | Thermal Resistance of Junction-to-Case [°C/W]                        |

| $R_{da}$       | Thermal Resistance of Heatsink-to-Ambient [°C/W]                     |

| $T_{hs}$       | Heatsink Temperature [°C]                                            |

| $C_{oss}$      | IGBT Output Capacitance [F]                                          |

| $\phi_{ZVS,P}$ | Minimum Phase-shift Required for ZVS [rad]                           |

| $P_{ZVS,P}$    | Minimum Power Required for ZVS [W]                                   |

| $L_{dab,meas}$ | External Inductance Measured [H]                                     |

| $L_{meas}$     | Total Inductance Measured [H]                                        |

|                |                                                                      |

$\phi_{R,new}$  Adjusted Rated Phase-Shift [rad]

$v_{ab}$  Alternating Component of Voltage  $v_{ab}$  [V]

$v_{cd}$  Alternating Component of Voltage  $v_{cd}$  [V]

$v_{ab\sim,rms}$  RMS Value of Voltage  $v_{ab\sim}$  [V]

$v_{cd\sim,rms}$  RMS Value of Voltage  $v_{cd\sim}$  [V]

$v_{ce,P1}$  Collector-Emitter Voltage of Power Switch P<sub>1</sub> [V]

$v_{be,P1}$  Base-Emitter Voltage of Power Switch P<sub>1</sub> [V]

$I_S$  Average Value of the Input Source Current [A]

$i_{Ro}$  Load Current [A]

$I_{1,sec}$  Switching Current  $I_1$  Referred to Secondary Side [A]

$I_{2.sec}$  Switching Current  $I_2$  Referred to Secondary Side [A]

$I_{Ro}$  Average Value of Load Current [A]

$\phi_{int}$  Internal Phase-Shift [°]

$I_{zp}$  Zero Active Power Current [A]

$\Delta T_{zp}$  Zero Active Power Period [s]

$I_{L,pk}$  Peak Value of Inductor Current [A]

$P_{ref}$  Reference Value for Power Transmitted [W]

$\phi_i$  Initial Value of External Phase-shift [°]

$\phi_f$  Final Value of External Phase-shift [°]

$\phi_{int,i}$  Initial Value of Internal Phase-shift [°]

$\phi_{int.f}$  Final Value of Internal Phase-shift [°]

$\Delta \phi$  Step Value of External Phase-shift [°]

$\Delta \phi_{int}$  Step Value of Internal Phase-shift [°]

$V_{o,ref}$  Reference Value for Output Voltage [V]

$V_{tol}$  Tolerance Voltage for mCSPT [V]

$T_w$  Waiting Period for mCSPT [s]

$S_i$  Input Apparent Power [VA]

$S_{i,b}$  Base Value of Input Apparent Power [VA]

$\overline{S}_{l}$  Normalized Input Apparent Power [p.u.]

S<sub>o</sub> Output Apparent Power [VA]

Q Reactive Power [var]

D Distortion Power [VA]

N Non-Active Power [VA]

$N_i$  Input Non-Active Power [VA]

$Q_i$  Input Reactive Power [var]

∀ For All

$\Lambda$  And

# **CONTENTS**

| 1     | INTRODUCTION                   | 15 |

|-------|--------------------------------|----|

| 1.1   | GENERAL GOAL                   | 18 |

| 1.2   | SPECIFIC GOALS                 | 18 |

| 1.3   | CONTRIBUTIONS                  | 19 |

| 1.4   | THESIS SCOPE                   | 19 |

| 1.5   | THESIS STRUCTURE               | 20 |

| 2     | LITERATURE REVIEW              | 22 |

| 2.1   | TOPOLOGY OVERVIEW              | 23 |

| 2.2   | MODULATIONS                    | 24 |

| 2.2.1 | Single Phase-Shift             | 25 |

| 2.2.2 | Extended and Dual Phase-Shift  | 27 |

| 2.2.3 | Triple Phase-Shift             | 28 |

| 2.2.4 | Other Modulations              | 29 |

| 2.3   | MODELLING                      | 31 |

| 2.4   | SOFT-SWITCHING                 | 32 |

| 2.5   | VARIABLE VOLTAGE APPLICATIONS  | 33 |

| 2.6   | MAGNETICS DESIGN               | 34 |

| 2.7   | TRANSFORMER SATURATION         | 35 |

| 2.8   | HARDWARE OPTIMIZATION          | 37 |

| 2.9   | HIGH-POWER PROTOTYPES          | 37 |

| 3     | SINGLE PHASE-SHIFT MODULATION  | 40 |

| 3.1   | TOPOLOGICAL STAGES             | 41 |

| 3.2   | MAIN WAVEFORMS                 | 45 |

| 3.3   | MATHEMATICAL ANALYSIS          | 48 |

| 3.3.1 | Power Transmission             | 49 |

| 3.3.2 | Inductor Current               | 54 |

| 3.3.3 | Input and Output Currents      | 58 |

| 3.3.4 | Circulating Power              | 59 |

| 3.3.5 | Transformer VA Rating          | 65 |

| 3.3.6 | Semiconductors Stresses        | 70 |

| 3.3.7 | Passive Components Computation | 73 |

| 3.3.8 | Dead-time Effect               | 81 |

| 3.3.9    | Soft-switching Operation                             | 82     |

|----------|------------------------------------------------------|--------|

| 3.3.10   | Final Remarks                                        | 90     |

| 4        | PROTOTYPE DESIGN                                     | 92     |

| 4.1      | REQUIREMENTS                                         | 92     |

| 4.2      | DESIGN METHODOLOGY                                   | 95     |

| 4.2.1    | Transformer                                          | 97     |

| 4.2.2    | Additional Inductor                                  | 98     |

| 4.2.3    | DC Blocking Capacitors                               | 100    |

| 4.2.4    | Output Capacitor                                     | 101    |

| 4.2.5    | Semiconductors Stresses                              | 101    |

| 4.2.6    | Soft-Switching Limits                                | 104    |

| 4.2.7    | Parameters Corrections                               | 106    |

| 4.3      | FINAL ASSEMBLY OF THE PROTOTYPE                      | 107    |

| 5        | EXPERIMENTAL VALIDATION OF THE PROTOTYPE             |        |

| 5.1      | MAIN WAVEFORMS                                       | 110    |

| 5.2      | ESTIMATED AND MEASURED RESULTS                       | 115    |

| 5.3      | EFFICIENCY OF THE POWER STAGE                        | 119    |

| 5.4      | OPERATION POINTS OUT OF ZVS REGION                   | 121    |

| 6        | DUAL PHASE-SHIFT MODULATION                          | 123    |

| 6.1      | OPERATION OVERVIEW                                   | 123    |

| 6.2      | CURRENT STRESS UNDER THE CONDITION $\phi < \phi int$ | 127    |

| 6.2.1    | Final Remarks                                        | 129    |

| 6.3      | ALGORITHM PROPOSAL                                   | 130    |

| 6.3.1    | Description of the Algorithm Operation               | 131    |

| 6.3.2    | Simulation                                           | 135    |

| 6.3.3    | Experimental Setup                                   | 139    |

| 6.3.4    | Experimental Results                                 | 142    |

| 7        | CONCLUSION                                           | 148    |

|          | REFERENCES                                           | 151    |

|          | APPENDIX A - FURTHER MATHEMATICAL ANALYSIS           | OF SPS |

|          | MODULATION                                           | 159    |

| A.1 INPL | UT APPARENT AND NON-ACTIVE POWER                     | 159    |

| A.2 SEM  | IICONDUCTORS CURRENT STRESS                          | 161    |

| A.3 OUTPUT CAPACITOR167                           |

|---------------------------------------------------|

| APPENDIX B – EQUIPMENT FOR EXPERIMENTAL TESTS169  |

| APPENDIX C - MORE WAVEFORMS OF DPS MODULATION     |

| INVESTIGATION170                                  |

| APPENDIX D - SIGNAL CONDITIONING BOARD DESIGN     |

| METHODOLOGY172                                    |

| APPENDIX E - DSP CODE ALGORITHM IMPLEMENTATION175 |

|                                                   |

# 1 INTRODUCTION

Amid environmental concern and rising global temperatures due to human activities (Copernicus, 2025), replacing technology that relies on fossil fuel – coal, oil and natural gas, which contributes to climate change (IPCC, 2021) – with "greener" alternatives is paramount to prevent even higher temperatures and preserve life on the planet (IPCC, 2018).

Electricity generated by coal and natural gas still represents around half of the world's generation (IEA, 2024a). Even though there has been significant growth recently, renewable energy must be tripled by 2030 to keep on track of the goals defined in the Paris Agreement (IEA, 2023a). In the next years, solar and wind energy are expected to represent most of the new installed capacity of all renewable energies (IEA, 2024b).

In this context, some emerging technologies are promising in society's quest to attain a cleaner future with renewable energy, such as Electric Vehicles (EV) and Battery Energy Storage Systems (BESS). Although these concepts have already been presented in the past, only now they are financially viable for implementation, especially due to recent advances that allows for cheaper, smaller and lighter batteries.

Solar and wind are better utilized if linked to BESSs, given its intermittent nature: solar energy is only converted during the day and wind energy can only be converted when there is enough wind to turn the turbines. Storing this energy for usage when nothing can be generated or if excess energy is converted is essential. Moreover, BESSs can help ease the grid during high demand peaks (Segaran, 2013). The International Renewable Energy Agency (IRENA) estimates it will be necessary around 359 GW of capacity from BESSs around the world by 2030 to fulfill Paris Agreement's goals (IRENA, 2023).

EVs use electric motors, meaning there is zero carbon emission when driving (provided that the electricity comes from renewable energies). It is also much more efficient than internal combustion engine cars, which depend on oil. In 2022, global EV sales were slightly more than 10 million. However, to reach carbon emission goals, sales in 2030 should be around 59 million, corresponding to a 67% share of global vehicle sales (IEA, 2024c).

EVs can be viewed as mobile BESSs, meaning the energy stored in the batteries can be used for other applications, like injecting it back to the grid - known as Vehicle to Grid (V2G) - or supply power to an electrical equipment (Safayatullah *et al.*, 2022).

To enable EVs as the main type of transportation, improvements on the grid must be made to deal with the larger power peak demand. Furthermore, fast charging stations of high power must be installed in cities, highways and countryside, to guarantee that EVs can be recharged faster during a long trip, compared to low power recharging of residences, workplaces and commercial buildings that takes hours to fully recharge (Safayatullah *et al.*, 2022; Jung, 2017).

Wind turbines generate electricity in Alternate Current (AC) but must be rectified into Direct Current (DC) to deal with variable frequency caused by the unpredictable nature of the wind. Solar panels generate electricity in DC. In this manner, the use of renewable energy can promote the development of DC transmission and distribution networks, increasing the efficiency in a system where most sources and loads are of DC nature (Ertugrul, 2024).

DC grids facilitate the connection of different sources on the grid, since there is no need for phase/frequency synchronism, although the short circuit detection and extinction gets harder (Dujic, 2023). Moreover, DC grids may use only two conductors (instead of three in a three-phase AC grid), which reduces the amount of copper used in transmission lines, since an increase in its demand is expected (IEA, 2023b, 2023c).

Power Electronics plays a key role in this energy transition. Most of the world's electricity runs through power converters (Ertugrul, 2024), since each equipment/application has different requirements of voltage and current. Essentially, power converters interface sources and loads to adequate voltage/current levels or type (AC/DC) between them, which is done by controlling the electrical current flow. Thus, making sure loads can be powered properly.

Improving power converters leads to several benefits for society: higher efficiency means less electrical energy loss and smaller batteries needed; reduction in volume, weight and number of components means less materials used; better reliability means less components are damaged and longer converter/equipment availability.

As for the emerging technologies mentioned previously, a DC-DC converter is crucial for enabling their operation. This converter takes a DC voltage from an input source and can step up or step down the voltage level to the output load. Equal input and output voltages are also possible.

Furthermore, these converters can offer galvanic isolation by utilizing medium/high frequency transformers (> 1 kHz), resulting in much lighter and smaller transformers than the low frequency transformer (50/60 Hz), providing safety to users (Zhao *et al.*, 2014; Kenzelmann *et al.*, 2015).

For BESSs, a bidirectional DC-DC converter, which allows current to flow in both ways, is used to adequate voltage levels between the system and the grid, as well as allowing charging and discharging of the batteries.

In EVs, DC-DC converters are used to charge the batteries and to provide a DC bus for the traction inverter and other auxiliary loads, like electronic control units and sensors. Low power charging is done by the on-board charger, in which high power density is required. For high power charging (>20 kW), the charger is off-board, meaning it is located outside the vehicle, i.e., in the fast charging station (Safayatullah *et al.*, 2022).

If the charger is unidirectional, it is only possible to supply energy from the grid to the vehicle, known as Grid to Vehicle (G2V), because the current can only flow in one direction. To use the energy stored in the batteries for other purposes, e.g., V2G mode, a bidirectional converter must be used. Galvanic isolation is desired for meeting safety standards, either for on-board or off-board chargers. Storing energy from regenerative breaks also requires a bidirectional converter (Safayatullah et al., 2022).

DC grids require bidirectional DC-DC converters to interface the multiple energy sources (wind, solar, fuel cell), energy storages (batteries, supercapacitors) and loads (Segaran, 2013). Galvanic isolation is also desirable for interconnecting different DC grids.

More Electric Aircrafts (MEA) may have their own DC microgrid. This system is composed of generators, loads and energy storage systems (batteries, supercapacitors). Hence, bidirectionality is essential to manage the power flow. Galvanic isolation is also required by standards, such as the MIL-STD-704F. High

power density is vital for aircrafts (and other EVs), since it has very limited space and weight capacity (Buticchi; Costa; Liserre, 2017).

In this context, the Dual Active Bridge (DAB) is a DC-DC converter that stands out. Initially, it was proposed for aerospace power systems. However, research interest in the converter has skyrocketed because of its main characteristics: bidirectionality, galvanic isolation, modularity, inherent soft switching, high power processing and high power density, making it a suitable choice for the emergent technologies (De Doncker; Divan; Kheraluwala, 1991; Zhao *et al.*, 2014). Thus, it is chosen as the subject for this Master's thesis.

The bigger challenges that need to be overcome for consolidation of the DAB converter are the large reactive power and loss of soft switching when the converter operates with a wide voltage range and under light load, which reduces efficiency (Shao *et al.*, 2019), although this problem is inherent to any converter that operates with soft switching.

# 1.1 GENERAL GOAL

There are two general goals for this Master's thesis: the first one is to establish an academic reference with a comprehensive and easy to understand analysis that covers all of the important aspects of the DAB converter. The second one is to develop an algorithm using Dual Phase-Shift modulation to minimize the current stress in the transformer and in the power switches for evaluation of the converter efficiency. Also, it should be easy to implement.

# 1.2 SPECIFIC GOALS

The specific goals established for achieving the general goals are:

- Research the design challenges of the DAB converter considering different applications.

- Analyze the circuit operation of the converter employing the simplest modulation (Single Phase-Shift).

- Verify important aspects such as transformer apparent power, circulating power and soft-switching operation and their impact on the converter operation.

- Establish a mathematical model for the design of the main components of the converter.

- Build and test a prototype to verify if the experimental measurements match the operation described theoretically.

- Analyze the operation of the converter employing the Dual Phase-Shift modulation.

- Investigate the impact of the control variables on the transformer current when the converter operates in a condition when there is a period with no active power being transferred.

- Propose, develop and experimentally test a way to automatically reduce the current stress in the transformer and in the power switches.

# 1.3 CONTRIBUTIONS

The contribution of this Master's thesis is summarized as follows:

• Proposes a simple and automatic digital algorithm for reducing the current stress in the transformer and power switches for the Dual Phase-Shift modulation.

# 1.4 THESIS SCOPE

The research and study done in this Master's thesis is limited by the following points:

• The topology of the Dual Active Bridge converter for the literature review and the circuit analysis is the single-phase, voltage fed and non-resonant topology, with the active bridge configuration being a standard full-bridge.

- The theoretical analysis of the converter considers only ideal components. Parasitic components are not considered in any equation derived (except for soft-switching).

- The thesis does not provide analyses and neither equations for designing and building the magnetic components of the converter.

- The algorithm proposed is developed and tested for the specific condition of when the external phase-shift is lower than the internal phase-shift of the Dual Phase-Shift modulation. Moreover, it is supposed to be used as an additional feature for the main control system of the converter, since it needs initial input values. Lastly, the algorithm is supposed to execute when the converter is operating in steady-state, and for the sake of simplifying the tests, it does not detect if the load changes during its execution.

# 1.5 THESIS STRUCTURE

The next chapters of this thesis have the following content:

Chapter 2 presents a review of many papers read during the study of the DAB converter, mixing the converter's characteristics and state-of-the-art techniques published. It is intended as an overview of various important topics, so the reader can have a glimpse of some aspects regarding the converter's operation in a qualitative manner.

Chapter 3 presents a detailed analysis of the fundamental concepts for the DAB converter, considering Single Phase-Shift modulation. Mathematical expressions for many converter parameters are derived for understanding and aiding the converter design.

Chapter 4 presents the design methodology of a 600 W prototype for experimental validation of the circuit analysis presented in previous chapters. The converter is designed for a 380 V to 380 V voltage conversion. Besides the main equations for designing the converter, the chapter contains the technical specifications of the active bridge PCBs and magnetics used for building the prototype.

Chapter 5 presents the experimental results of measurements done with the prototype designed in the previous chapter. Voltages and current waveforms are presented for confirming the converter operation as described in Chapter 3, as well as tables for comparing theoretical results and experimental measurements. The estimated efficiency of the converter is also compared with the measured efficiency.

Chapter 6 starts with a brief description of the Dual Phase-Shift modulation applied to the DAB converter. After that, an investigation is done for a specific operation condition of the Dual Phase-Shift modulation where there is a period when no active power is transferred between the input and output voltage sources. The results obtained from such investigation inspired the development of an algorithm for minimizing the current stress of the converter when operating in this condition of the Dual Phase-Shift modulation. A comprehensive description of the proposed algorithm is done, with simulation and experimental results for showing the operation of the algorithm and proving that its goal of minimizing current stress is achieved.

Chapter 7 ends the Master's thesis with the final conclusions of the work done with suggestions for future work regarding the algorithm proposed.

# 2 LITERATURE REVIEW

In this section, the literature is reviewed to get familiar with the converter's fundamental concepts, the challenges of its design and the state-of-the-art techniques shared by other researchers.

The Dual Active Bridge converter was proposed by De Doncker; Divan; Kheraluwala (1991), both single-phase and three-phase topologies, for use in applications that need high power and high power density. In the three-phase version, much higher power can be processed, since currents are better distributed between magnetics, input/output filter capacitors are smaller and output current ripple is reduced (Li *et al.*, 2023; Safayatullah *et al.*, 2022). However, the single-phase version has a simpler design, lower cost and can achieve comparable power capacity by combining other modules.

The DAB converter did not receive much attention in its early years after it was proposed in 1991 (Zhao *et al.*, 2014), but has been gaining a lot of interest from the academy since 2015 (Kenzelmann *et al.*, 2015; Li *et al.*, 2023), due to the development of better semiconductors and desirable characteristics for trending technologies (Zhao *et al.*, 2014). Prototypes reported in the literature have rated power up to 500 kW. Potential applications for the DAB are:

- Renewable Energy (Friedemann; Krismer; Kolar, 2012);

- DC Grids / Smart Grids (Song et al., 2020; Segaran, 2013);

- Electric Vehicles (terrestrial) (Yan et al., 2020);

- MEAs (Buticchi; Costa; Liserre, 2017; Naayagi; Forsyth; Shuttleworth, 2012);

- Solid State Transformers (SST) (Heinig et al., 2022; Xu et al., 2020).

This review covers a wide range of topics important for converter design, like: modulation strategies, optimization, magnetics, modelling, wide bandgap semiconductors and topological modifications.

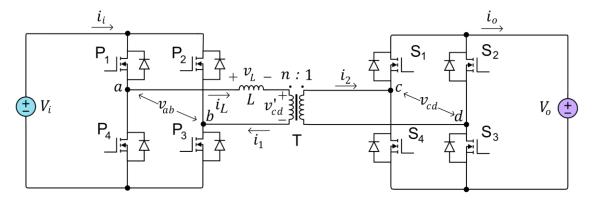

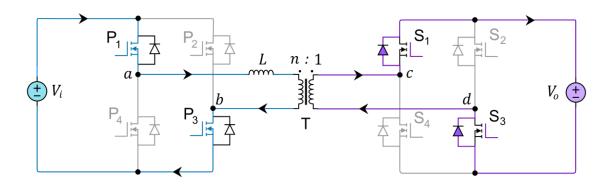

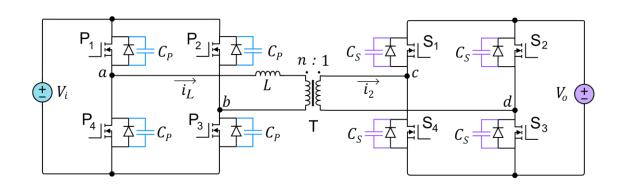

The scope of this review is limited to single-phase topologies. In this work, the "conventional DAB" is defined as the single-phase topology proposed by De Doncker; Divan; Kheraluwala (1991): composed by H-bridges (full-bridges), voltage-fed and non-resonant. Figure 1 presents the topology.

Figure 1 – Topology diagram for the conventional DAB.

Source: provided by the author, 2024.

Below are some terms' definitions for ease of understanding the concepts of the converter and explanations in this chapter:

- "Voltage conversion ratio" or "Voltage ratio": means the ratio between input and output voltage referred to the same side of the transformer. For example, if both voltages are referred to the primary, then the voltage conversion ratio is  $K = nV_o/V_i$ , where n is the turns ratio of the transformer,  $V_i$  is the input voltage and  $V_o$  is the output voltage. Not to be confused with DC-DC conversion;

- Voltage match: when the voltage ratio is unitary (or close to unity);

- ZVS region: group of operating points depending on voltage ratio, phase-shift or power transmitted that enables ZVS operation of the converter;

- Reactive/circulating/backflow power: is defined as the portion of instantaneous power that goes back to the input source and does not contribute to active output power;

- Current stress: peak and RMS values of the inductor current.

# 2.1 TOPOLOGY OVERVIEW

The conventional DAB has an input and an output capacitor, two active Hbridges separated by a transformer in series with an inductor. The two bridges make it possible to control power flowing in both directions and achieving high levels of power. The transformer provides galvanic isolation and allows buck-boost operation. The inductor serves as the instantaneous energy storage component (Zhao *et al.*, 2014). The idea is that the leakage inductance of the transformer is used as the inductor, improving the power density of the converter, whereas an external inductor would compromise the power density, reliability and increase costs (but can be used as well). Natural soft switching by Zero Voltage Switching (ZVS) is achieved by using resonance between the parasitic output capacitance of the power switches and the inductor (De Doncker; Divan; Kheraluwala, 1991).

The main converter's losses can be divided between two components: the transformer and the switching devices. In the transformer, there are copper losses and core losses. In the switching devices, there are conduction losses and switching loss (Kim *et al.*, 2011).

Both copper and conduction losses depend on the RMS value of the current. The reactive power is responsible for increasing the RMS value of the current without increasing the active power transmitted (Kim *et al.*, 2011).

The core losses are dependent on the magnetic flux density, which depends on the net voltage-seconds applied, which in turn depends on the peak value of the current. Of course, switching frequency also impacts core losses (Kim *et al.*, 2011).

The switching losses are dependent on the switching frequency, voltage across the power switch and peak value of the current (Kim *et al.*, 2011).

In the last 10 years, there have been over 200 papers proposing topological/hardware modifications for the DAB, such as: different active bridges, transformers, inductors, resonant components, multiport input/output and many others. Both voltage-fed and current-fed topologies are possible (Li *et al.*, 2023).

# 2.2 MODULATIONS

The modulation strategy chosen for the converter can impact several aspects of its operation. Common optimization goals are: minimum RMS value of current, minimum reactive power, minimum current stress (Kim *et al.*, 2011), ZVS

range, efficiency under light load and transformer DC bias elimination (Li *et al.*, 2023; Corti *et al.*, 2022).

Traditional modulation strategies for the conventional DAB converter are the phase-shifted Pulse Width Modulations (PWM) (Corti *et al.*, 2022). The duty cycle of the driving signals is always fixed in 50%. There are usually two types of phase-shifts:

- External/outer phase-shift: the phase-shift between the output voltages of the primary and secondary bridges. This is done by adding a phase-shift in the PWM's carrier signal of one bridge with respect to the carrier of the other bridge. The leading voltage is the one delivering power.

- Internal/inner phase-shift: the phase-shift between driving signals

in a pair of power switches from the bridge. The addition of the

inner phase-shift leads to a 3-level voltage waveform in the output

of the bridge, allowing to adjust its duty cycle. Sometimes this

parameter is defined in terms of the duty cycle from the output

voltage waveform of the active bridge.

It is also important to note that, some authors define different references for the phase-shift. Some common choices are: at the start of the active period, at the middle of the active period or at the fundamental component of the voltage. The reference chosen might impact in the form of the equations for the parameters of the converter, which can be confusing. Obviously, all of them should compute the same value.

As the number of phase-shifts (i.e., control variables) increases, the better the converter's performance can be optimized. However, the complexity of modelling and control implementation also increases.

# 2.2.1 Single Phase-Shift

The simplest modulation strategy is the Single Phase-Shift (SPS), which consists of the external phase-shift only. The waveform of the output voltage from both bridges is 2-level only. This modulation can only control the active power

transmission of the converter and achieves good efficiency rates when the voltage conversion ratio is close to unity (Corti et al., 2022).

Since it cannot control reactive power, which increases when there is no voltage match, the efficiency is reduced because of increased current stress (Corti et al., 2022; Liu; Sun; Liu, 2022).

Dead-time reduces the active power transmitted. This effect can be compensated by adding a value to the phase-shift reference proportional to the deadtime period, resulting in a bigger phase-shift value needed than the ideal case with no deadtime for the same output active power (Bai; Mi, 2008; Segaran, 2013).

The start-up process using SPS is a critical issue for the converter. If the output voltage is already relatively high on start-up, but it is still not the reference value, the phase-shift should be incremented slowly until it reaches the rated value required for that operation point. This way, the peak value of the inductor current during start-up is minimized (Bai; Mi, 2008). However, if the output voltage is zero, the inductor current cannot be limited, whether it is a hard start or soft start, leading to a large inrush current that could damage the converter. Therefore, in this case it is recommended to use another modulation strategy, since other methods to address this issue would be:

- a) increase the input voltage from zero;

- b) precharge the output capacitor;

- c) utilize components that withstand bigger current stress (Bai, Mi, 2008).

Naayagi, Forsyth and Shuttleworth (2012) presented an analysis of the converter during steady-state, providing essential equations for its hardware design and loss estimates, such as RMS value of the inductor current and RMS and average values of the semiconductors' current, considering both buck and boost modes of operation (i.e., bidirectional power flow).

Moreover, the impact of snubber capacitors installed across the switches on the ZVS operation of the converter is studied. Experimental tests with a prototype processing 7 kW show that the results of proposed equations are similar to measured values.

#### 2.2.2 Extended and Dual Phase-Shift

Extended Phase-Shift (EPS) and Dual Phase-Shift (DPS) modulations were introduced to minimize the reactive power and increase the ZVS range when there is no voltage match or under light load. Aside from the external phase-shift, in EPS there is an internal phase-shift in only one of the bridges, whereas in DPS, both bridges have the same value of internal phase-shift applied (Corti et al., 2022). Although better than SPS, DPS still cannot achieve ZVS for all switches under light load (Yan et al., 2020).

DPS modulation in DAB converters was studied initially by Bai and Mi (2008). The definition of reactive power used is the instantaneous power sent back to the input source during its operation, which happens when the inductor current and the input voltage have different polarities. Other papers adopt the same definition for reactive power (Wang *et al.*, 2014; Shao *et al.*, 2019), however, it is important to remember that it does not account for all non-active power in the converter.

The reduction of reactive power also implies on the reduction of the output voltage ripple, since it is directly proportional to reactive power (Bai; Mi, 2008), and the reduction of current stress for the same amount of power transmitted, compared to SPS (Zhao; Song; Liu, 2012).

Furthermore, with DPS modulation, it is possible to soft-start the converter with zero output voltage without the need of additional circuits. The inrush current is significantly lower during the soft-start with DPS, in comparison with SPS modulation (Bai; Mi, 2008).

Experimental tests done by Bai, Nie and Mi (2010) confirmed that DPS can achieve higher efficiency than SPS when there is no voltage match (much less than unity) and under light-load conditions, but SPS can achieve higher efficiency when there is voltage match and under light-load or no voltage match (much higher than unity) and under heavy load conditions. Hence, it is recommended to use SPS during heavy-load and DPS under light-load operation for better efficiency across the power range of the converter.

An in-depth analysis made by Kim et al. (2011) provided equations for active power transmission, reactive power and RMS and peak values of the

inductor current for DPS. It also shows ZVS regions for different operation points. Limiting the external phase-shift to 90° reduces the following aspects: reactive power, RMS and peak value of inductor current. The equations provided allow for optimization of the control strategy to minimize these aspects, but only one can be chosen. Simulation and experimental tests with a 3.68 kW prototype show that the DPS modulation minimizing the peak value of the inductor current can result in higher efficiency for the whole power range than with SPS (application considered is an EV Charger).

According to Coelho and Batschauer (2021), comparing different modulation strategies by looking at the RMS value of the transformer current alone is not enough for estimating the best operation point. Neglecting the number of voltage levels applied to the transformer can lead to inaccurate estimates of its apparent power. Experimental results from different operation points using SPS, EPS and DPS are presented for confirmation.

## 2.2.3 Triple Phase-Shift

Triple Phase-Shift (TPS) modulation has the external phase-shift and two different internal phase-shift for each of the bridges in the converter, meaning three degrees of freedom for control. SPS, EPS and DPS can be seen as special cases from the TPS modulation. Since it is the most complete phase-shift modulation, the converter operating with TPS has the potential to achieve highest efficiency through the whole operation range (Corti *et al.*, 2022). It can achieve ZVS for all switches even under light load, however, switching-off current can increase (Yan *et al.*, 2020).

The Trapezoidal and Triangular Modulation Method proposed by Schibli (2000) shapes the inductor current waveform accordingly, in which the main goal is to reduce switching loss by modulating the current down to zero before turnoff, but it does not happen at every switching event. Trapezoidal Mode minimum power transmitted is the maximum power for Triangular Mode. A few drawbacks of this modulation are: it cannot be used if one of the bridges' output voltages is zero (or close to) or both equal (for triangular mode), unbalanced distribution of

losses (Schibli, 2000) and they could increase the RMS value of the inductor current (Kim *et al.*, 2011).

Krismer and Kolar (2012) presented a TPS modulation scheme optimizing the RMS value of the inductor current, decreasing conduction and copper losses. The converter operation is analyzed considering the fundamental component of the voltages. Closed form solutions are presented for the design. Under light load, the proposed modulation scheme falls into Triangular Current Modulation and under heavy load, into SPS. In medium power however, the operation results in complex equations, increasing control processing costs. Furthermore, the modulation scheme does not consider the ZVS conditions of the converter.

Huang *et al.* (2016) analyzes the TPS modulation considering all harmonic components of the voltages and presents an optimized modulation scheme to achieve minimum current stress. An auxiliar phase-shift is introduced between the fundamental component of the bridges' output voltages, which helps to define the direction of power flow. An optimization algorithm is implemented to deduce closed form solutions of the control variables. Under light load, the modulation scheme can also reduce the RMS value of the inductor current. Moreover, it is verified that the converter can operate with soft switching through the whole power range. The proposed optimization algorithm could be applied considering the minimization of any other parameter.

Table 1 resumes the traditional Phase-Shift (PS) strategies described in a conventional DAB. For this work, the name of the modulations refers to the types of phase-shifts used in it, since many modulation strategies (optimized) have been proposed based in these (as presented in this chapter).

#### 2.2.4 Other Modulations

Many other modulation strategies and optimizations have been proposed based on phase-shift for many applications, which may include other parameters like different duty cycles (asymmetric modulations) and variable switching frequency (He *et al.*, 2023).

For example, Taylor *et al.* (2018) proposed a modulation for on-board EV chargers that allows the DAB to function as a Power Factor Correction (PFC) and

Table 1 – Traditional Phase-Shift modulations comparison.

| Modulation                     | SPS  | EPS                   | DPS                    | TPS                        |

|--------------------------------|------|-----------------------|------------------------|----------------------------|

| External PS                    | Yes  | Yes                   | Yes                    | Yes                        |

| Internal PS                    | No   | Only in one<br>bridge | Equal for both bridges | Different for both bridges |

| Control<br>Variables           | 1    | 2                     | 2                      | 3                          |

| Voltage<br>Levels              | 2    | 2 and 3               | 2 and 3                | 2 and 3                    |

| Active Power<br>Control        | Yes  | Yes                   | Yes                    | Yes                        |

| Reactive Power and ZVS Control | No   | Limited               | Good                   | Best                       |

| Complexity                     | Easy | Medium Medium         |                        | Hard                       |

the DC-DC converter for transferring power. Basically, the modulation strategy uses a combination of DPS with variable switching frequency and TPS. When the input voltage (rectified grid voltage) is around its peak, the instantaneous transferred power is higher, in which the DPS modulation achieves higher

efficiency. When the input voltage is lower, TPS becomes the better option, since it can enable ZVS under light load. The use of DPS and TPS modulations allows to shape the input current waveform, achieving close to unity power factor from medium to high power, although the total harmonic distortion of the grid current is around 60% when under low power.

For high power DC grids, the use of Medium and High Voltage (MV and HV) is preferable to decrease losses through the line. In this case, the use of multilevel converters is recommended, because of the lower voltage stress on the power switches. Song *et al.* (2020) proposed an optimized modulation scheme for a DAB converter with a 5L NPC bridge on the high voltage port, which also allows for more degrees of freedom to shape the voltage waveform. Analytical solutions are developed for reducing the current stress, while considering the ZVS constraints. Simulations show that the modulation can achieve higher efficiency in the full power range even when there is no voltage match, in comparison to SPS.

#### 2.3 MODELLING

The simplest way to model a DAB converter is by utilizing the reduced order model, which doesn't consider the dynamics of the inductor current, resulting in a first-order model. This model is accurate enough for designing and implementing a voltage controller (Shao *et al.*, 2022).

An analysis for modelling the converter operating with SPS is done by Santos-Silva (2019), in which transfer functions are derived in both continuous and discrete domain for designing an output voltage controller. The designed controllers are validated using simulations in software and hardware-in-the-loop platforms.

In smart grids, a few requirements for power converters like galvanic isolation, bidirectionality and high performance regulation can be met by using the DAB converter. However, high performance voltage regulation design requires highly precise models of the converter. Segaran (2013) developed a dynamic model of the conventional DAB with SPS modulation considering all the harmonic components of the converter's operation. This way, the proposed

model can predict the switching nature of the converter. The analysis also takes into consideration the deadtime effects on dynamics and the power transmitted. The model can present a very similar behavior of the output voltage as seen in simulations of the converter. However, the inductor current equation of the model does not match the dynamic behavior of the simulation, only the steady state operation is accurate. Furthermore, the model can only predict transients caused by a minor phase-shift step (around 5°). Bigger steps of phase-shift require an adaptation of the model.

#### 2.4 SOFT-SWITCHING

The soft-switching in DAB converter depends on a few parameters: voltage conversion ratio, phase-shift angle, power switch output capacitance and magnitude and polarity of current on the switching instant (Kim *et al.*, 2011).

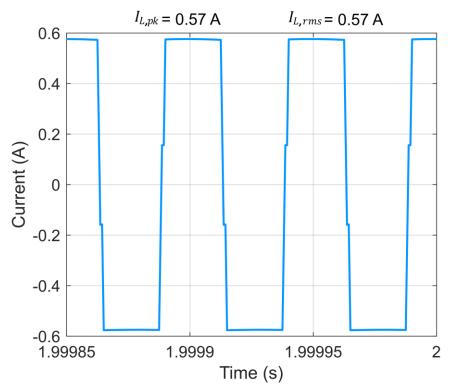

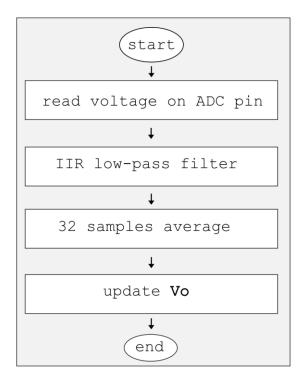

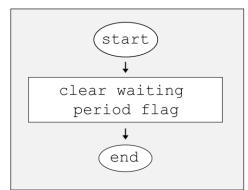

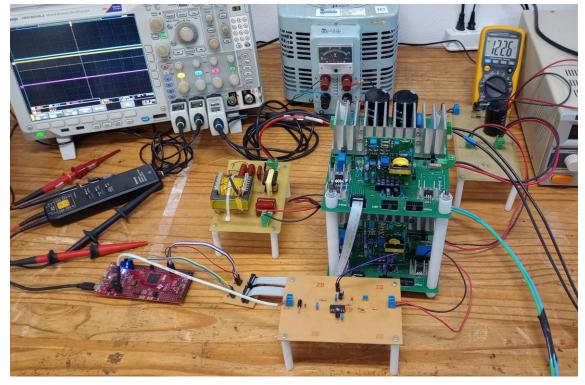

An analysis considering all harmonic components of the voltages is done by Riedel *et al.* (2017) to determine the ZVS region of the converter with more accuracy. It is found out that a simpler analysis considering only the fundamental component of the voltages leads to a smaller ZVS region than the full harmonic analysis, especially for low phase-shift values, where importance of higher harmonic components matters the most. The authors present expressions for analyzing the impact of various parameters, such as dead-time, parasitic output/snubber capacitors and different transformer impedances.